【導(dǎo)讀】在“為工業(yè)4.0啟用可靠的基于狀態(tài)的有線監(jiān)控——第1部分”一文中�����,我們介紹了ADI公司的有線接口解決方案�����,該方案幫助客戶縮短設(shè)計(jì)周期和測(cè)試時(shí)間��,讓工業(yè)CbM解決方案更快地進(jìn)入市場(chǎng)�����。本文探討了多個(gè)方面���,包括選擇合適的MEMS加速度計(jì)和物理層�����,以及EMC性能和電源設(shè)計(jì)��。此外���,還包括第一部分介紹的三種設(shè)計(jì)解決方案和性能權(quán)衡。本文為第二部分���,著重介紹第一部分展示的SPI至RS-485/RS-422設(shè)計(jì)解決方案的物理層設(shè)計(jì)考量��。

為MEMS實(shí)現(xiàn)有線物理層接口的常見挑戰(zhàn)包括管理EMC可靠性和數(shù)據(jù)完整性���。但是�����,在RS-485/RS-422長(zhǎng)電纜上分布SPI之類的時(shí)鐘同步接口���,同時(shí)在相同的雙絞線(虛假電源)上部署電源和數(shù)據(jù)時(shí)��,會(huì)帶來更多挑戰(zhàn)�����。本文討論以下關(guān)鍵問題��,并就物理層接口設(shè)計(jì)提供建議:

● 管理系統(tǒng)時(shí)間同步

● 推薦的數(shù)據(jù)速率與電纜長(zhǎng)度

● 適用于共用電源和數(shù)據(jù)架構(gòu)的濾波器設(shè)計(jì)和仿真

● 虛假電源結(jié)構(gòu)中的無源元件性能權(quán)衡

● 元件選擇和系統(tǒng)設(shè)計(jì)窗口

● 試驗(yàn)性測(cè)量

時(shí)間同步和電纜長(zhǎng)度

設(shè)計(jì)SPI至RS-485/RS-422鏈路時(shí)��,電纜和元件會(huì)影響系統(tǒng)時(shí)鐘和數(shù)據(jù)同步�����。在長(zhǎng)電纜中傳輸時(shí)��,SCLK信號(hào)會(huì)在電纜中產(chǎn)生傳播延遲�����,100米長(zhǎng)的電纜會(huì)延遲約400ns到500 ns�����。對(duì)于MOSI數(shù)據(jù)傳輸���,MOSI和SCLK會(huì)被電纜延遲同等時(shí)間�����。然而��,從從機(jī)MISO發(fā)送到主機(jī)的數(shù)據(jù)會(huì)出現(xiàn)兩倍傳播延遲�����,因而不再與SCLK同步�����?��?赡艿淖畲骃PI SCLK基于系統(tǒng)傳播延遲設(shè)置�����,包括電纜傳播延遲�����,以及主機(jī)和從機(jī)元件傳播延遲���。

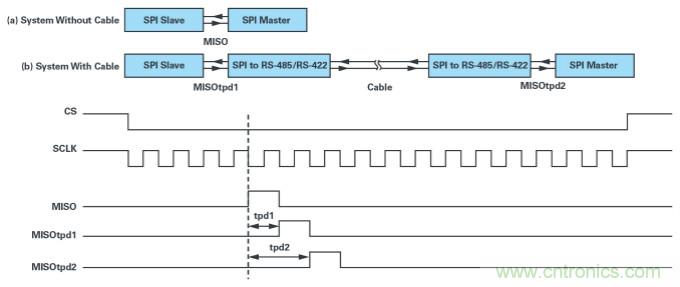

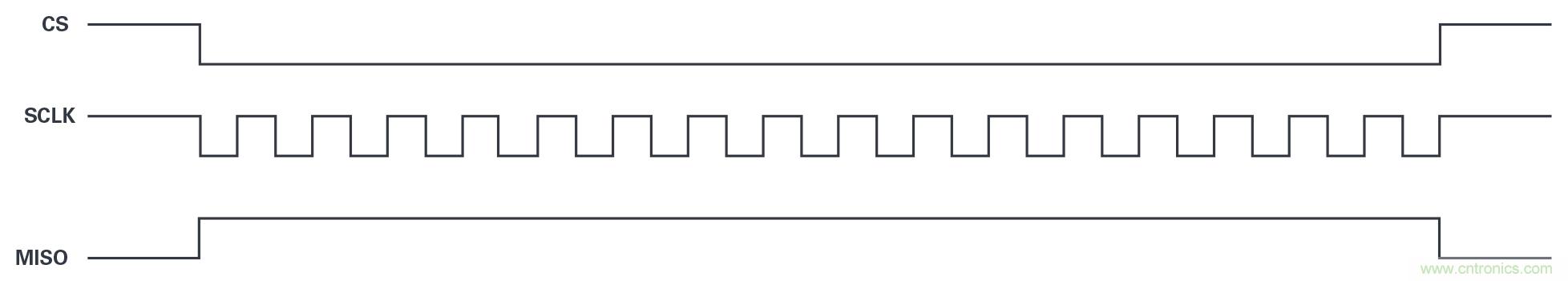

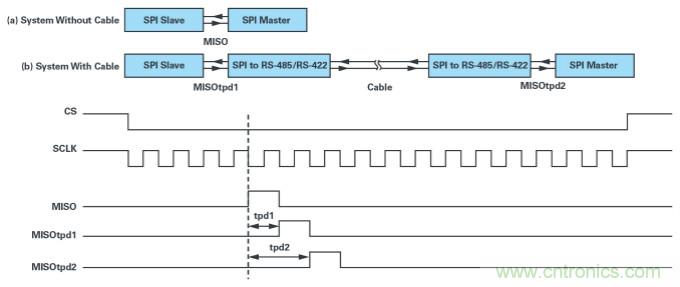

圖1展示系統(tǒng)傳播延遲如何導(dǎo)致SPI主機(jī)上出現(xiàn)不準(zhǔn)確的SPI MISO采樣。對(duì)于沒有采用RS-485/RS-422電纜的系統(tǒng)�����,MISO數(shù)據(jù)和SPI SCLK會(huì)以低延遲或無延遲同步���。對(duì)于采用了電纜的系統(tǒng)�����,SPI從機(jī)上的MISO數(shù)據(jù)與SPI SCLK之間存在一個(gè)系統(tǒng)傳播延遲��,如圖1中的tpd1所示�����?�;氐街鳈C(jī)的MISO數(shù)據(jù)存在兩個(gè)系統(tǒng)傳播延遲��,如tpd2所示��。當(dāng)數(shù)據(jù)由于電纜和元件傳播延遲而右移時(shí)���,會(huì)發(fā)生不準(zhǔn)確的數(shù)據(jù)采樣���。

圖1.采用與不采用RS-485/RS-422長(zhǎng)電纜的系統(tǒng)的MISO數(shù)據(jù)和SPI SCLK同步。

為了防止出現(xiàn)不準(zhǔn)確的MISO采樣���,可以縮短電纜長(zhǎng)度��、降低SPI SCLK�����,或者在主控制器中實(shí)施SPI SCLK補(bǔ)償方案(時(shí)鐘相位偏移)���。理論上,系統(tǒng)傳播延遲應(yīng)該小于SCLK時(shí)鐘周期的50%���,以實(shí)現(xiàn)無錯(cuò)通信���;在實(shí)踐中,可以將系統(tǒng)延遲限值確定為SCLK的40%��,這可以作為一般規(guī)則�����。

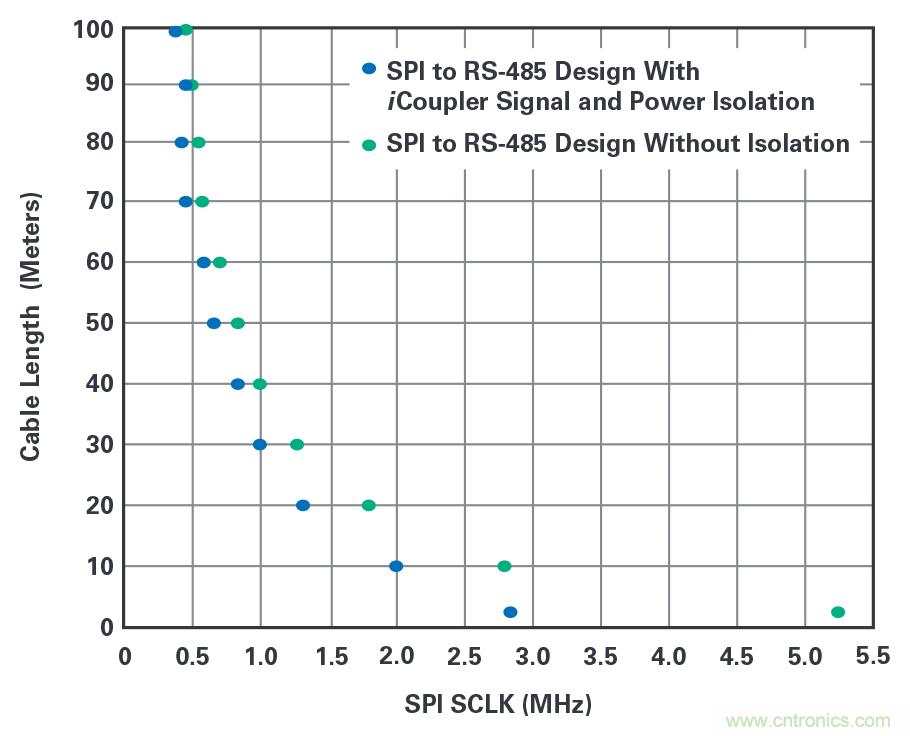

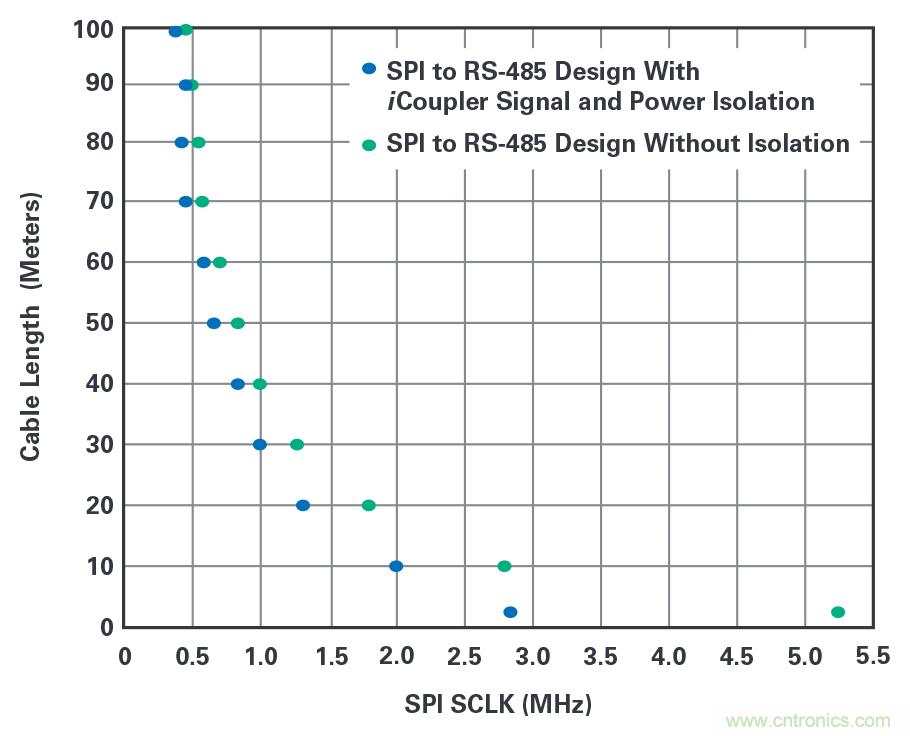

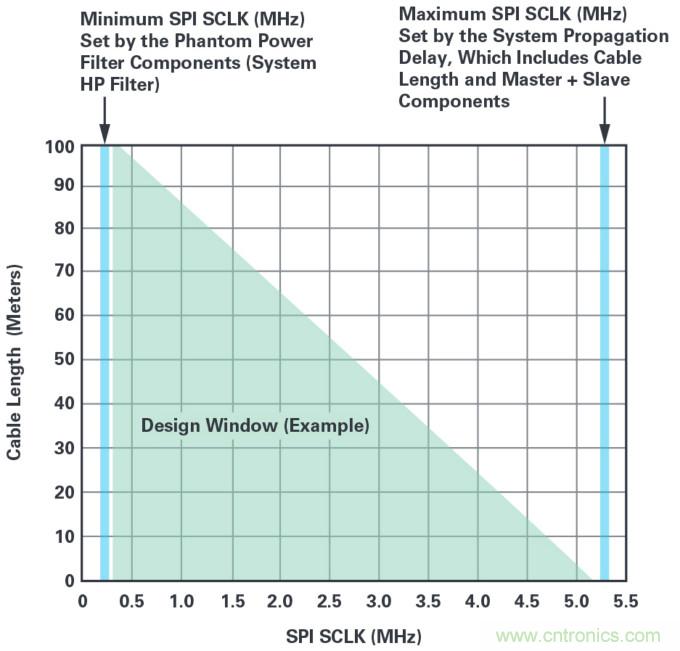

圖2針對(duì)1.1部分中描述的兩個(gè)SPI至RS-485/RS-422設(shè)計(jì)提供SPI SCLK和電纜長(zhǎng)度指南���。這種非隔離設(shè)計(jì)使用了ADI公司具備高速EMC穩(wěn)健性的小型RS-485/RS-422器件(ADM3066E和ADM4168E)���。這種隔離設(shè)計(jì)還采用了ADI公司的iCoupler®信號(hào)和電源隔離ADuM5401器件,可以為SPI至RS-485/RS-422鏈路提供更高的EMC穩(wěn)健性和抗噪聲干擾性能���。這種設(shè)計(jì)會(huì)增加系統(tǒng)傳播延遲��,導(dǎo)致不可在更高的SPI SCLK速率下運(yùn)行�����。在更長(zhǎng)的電纜(超過30米)中傳輸時(shí)��,強(qiáng)烈建議增加隔離�����,以幫助消除接地回路和EMC事件的影響�����,例如靜電放電(ESD)��、電快速瞬變脈沖群(EFT)�����,以及與數(shù)據(jù)傳輸電纜耦合的高壓浪涌���。當(dāng)電纜長(zhǎng)度達(dá)到或超過30米時(shí)��,隔離和非隔離設(shè)計(jì)的SPI SCLK和電纜長(zhǎng)度性能相似���,如圖2所示。

圖2.針對(duì)隔離和非隔離設(shè)計(jì)的SPI SCLK和電纜長(zhǎng)度指南�����。

虛假電源

背景知識(shí)

虛假電源將電源和數(shù)據(jù)部署在一根雙絞線上�����,在主機(jī)和從機(jī)之間實(shí)現(xiàn)單電纜解決方案��。將數(shù)據(jù)和電源部署在同一根電纜上,可以在空間有限的邊緣傳感器節(jié)點(diǎn)上實(shí)現(xiàn)單連接器解決方案���。

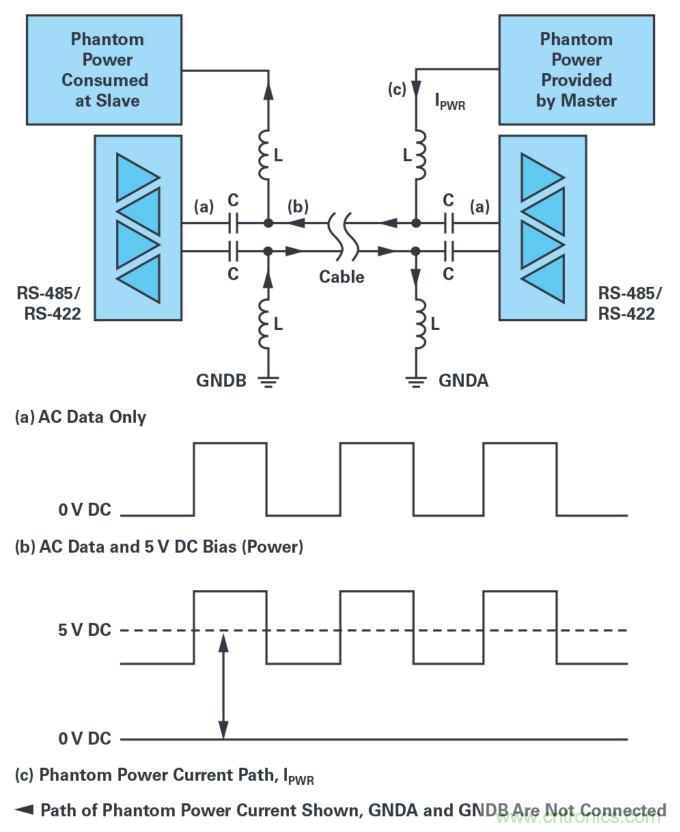

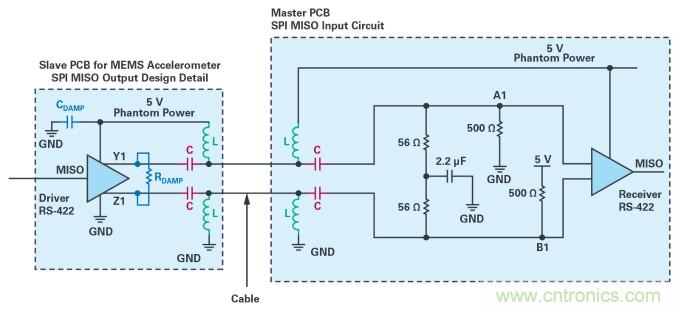

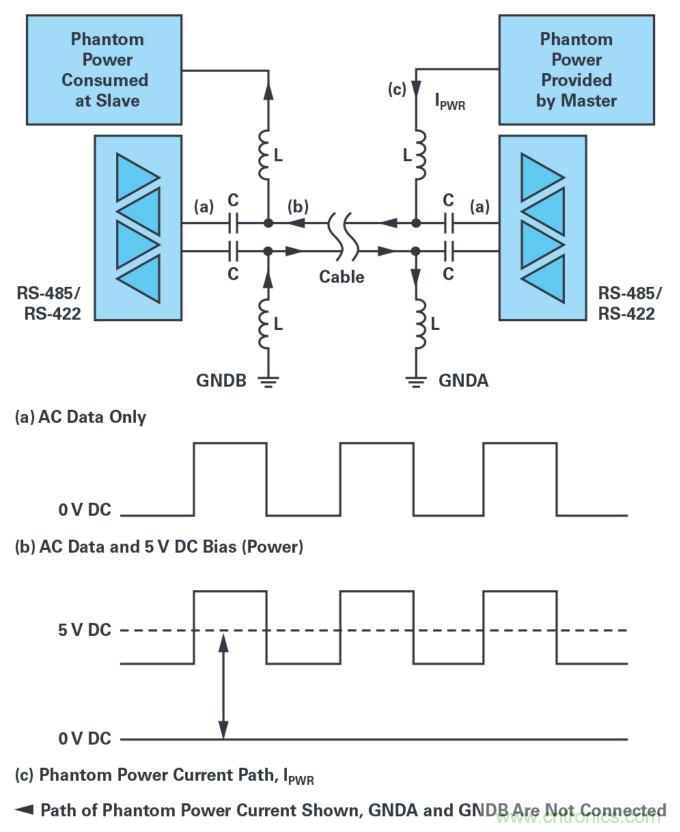

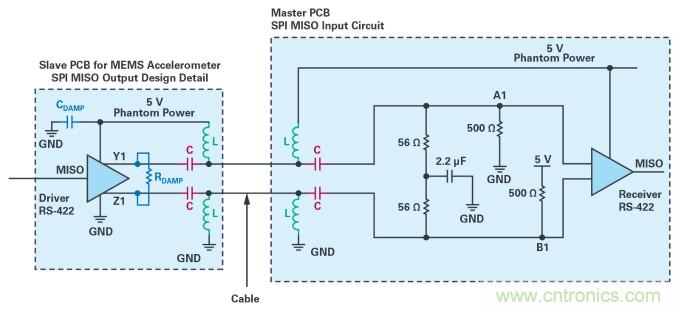

電源和數(shù)據(jù)通過電感電容網(wǎng)絡(luò)分布在單根雙絞線上��,具體如圖3所示�����。高頻數(shù)據(jù)通過串聯(lián)電容與數(shù)據(jù)線路耦合,可以保護(hù)RS-485/RS-422收發(fā)器免受直流總線電壓影響���,如圖3a所示��。圖3所示為通過連接至數(shù)據(jù)線路的電感連接至主機(jī)控制器的電源��。如圖3b所示���,5V直流電源對(duì)交流數(shù)據(jù)總線實(shí)施偏置。在圖3c中���,電流路徑顯示為從機(jī)和主機(jī)之間的IPWR��,使用電纜遠(yuǎn)端基于狀態(tài)監(jiān)控(CbM)的從機(jī)傳感器節(jié)點(diǎn)上電感從線路中獲取電源�����。

圖3.虛假電源物理層的交流和直流電壓電平�����。

高通濾波器

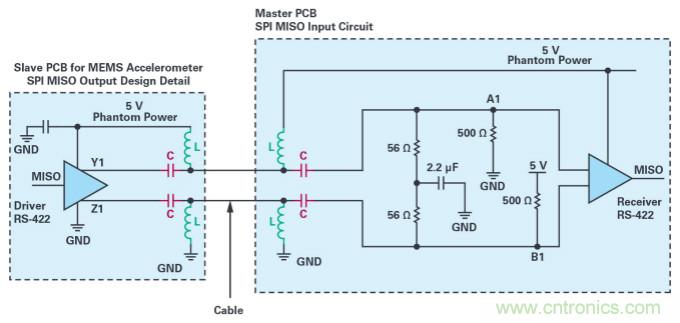

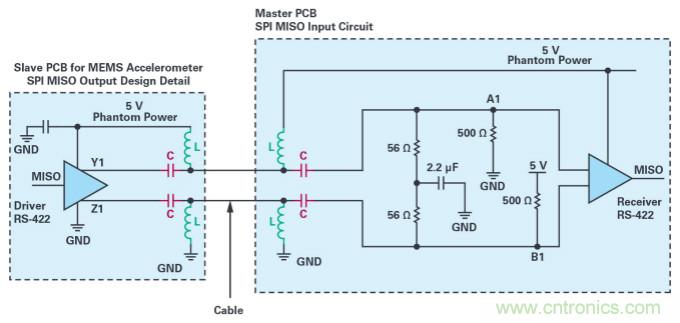

在本文中��,假設(shè)將虛假電源電感電容網(wǎng)絡(luò)部署到兩根電纜中��,這會(huì)部署SPI MISO信號(hào)的RS-485/RS-422轉(zhuǎn)換���。圖4描述主機(jī)和從機(jī)SPI至RS-485/RS-422的設(shè)計(jì)��,以及SPI MISO數(shù)據(jù)線的虛假電源濾波器電路���。濾波器電路采用高通電纜,所以要求傳輸?shù)臄?shù)據(jù)信號(hào)不能包含直流內(nèi)容或極低頻率的內(nèi)容���。

圖4.SPI至RS-485/RS-422設(shè)計(jì)和虛假電源濾波器電路���。

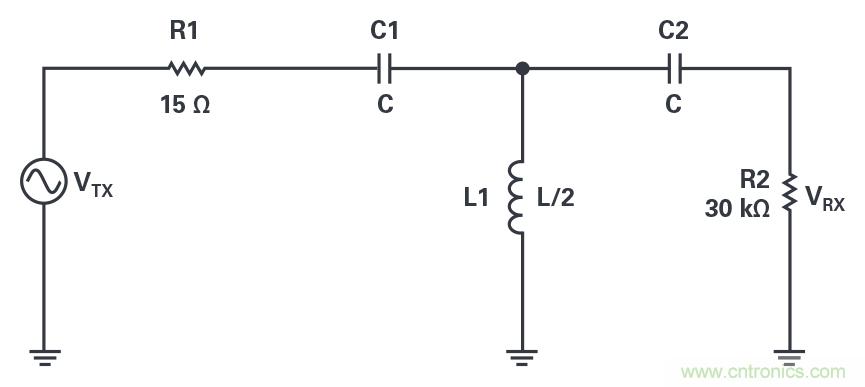

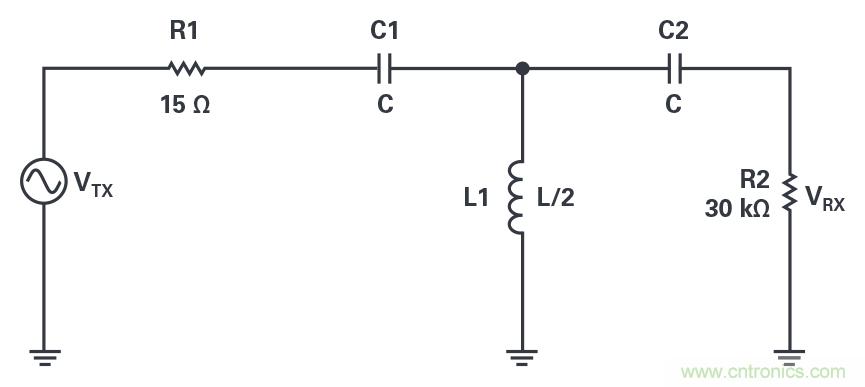

圖5所示為二階高通濾波器電路,這是對(duì)圖4的簡(jiǎn)化演示���。RS-485/RS-422發(fā)射器的電壓輸出標(biāo)記為VTX��,R1具備15Ω輸出電阻��。R2為30 kΩ���,是RS-485/RS-422接收器的標(biāo)準(zhǔn)輸入電阻���。電感(L)和電容(C)值可以選擇,以匹配所需的系統(tǒng)數(shù)據(jù)速率���。

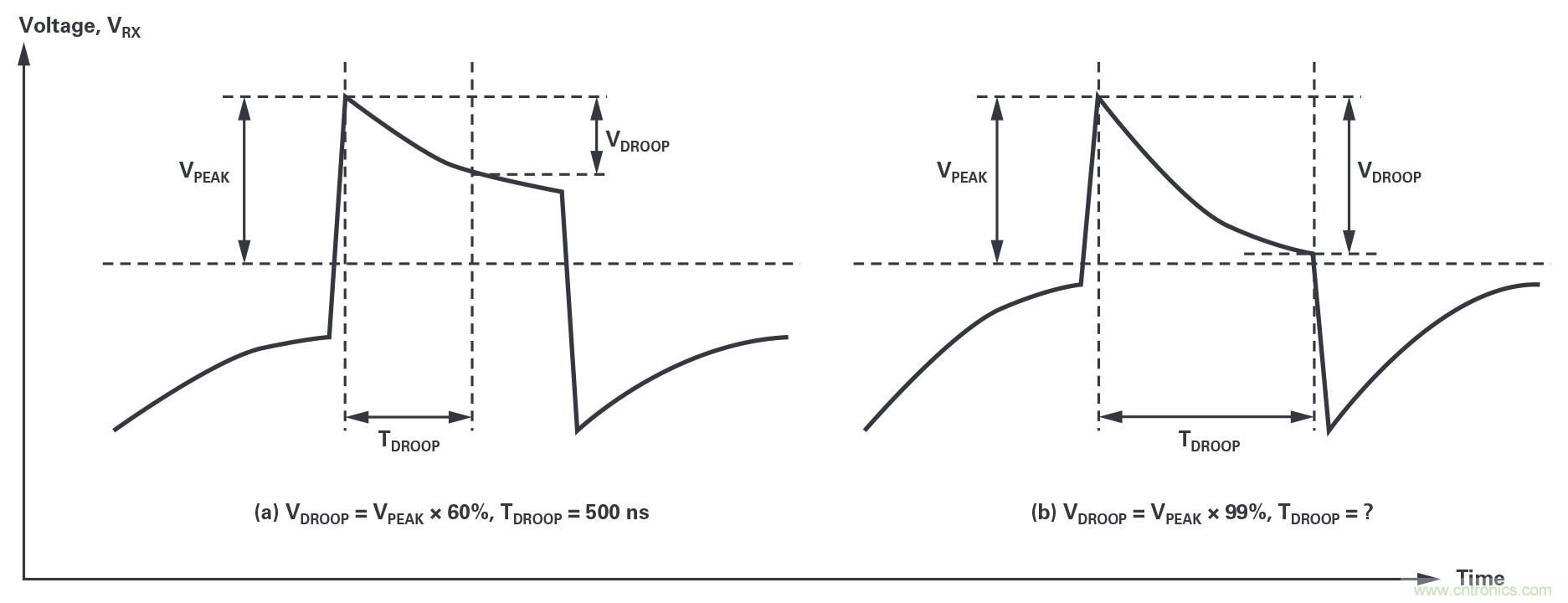

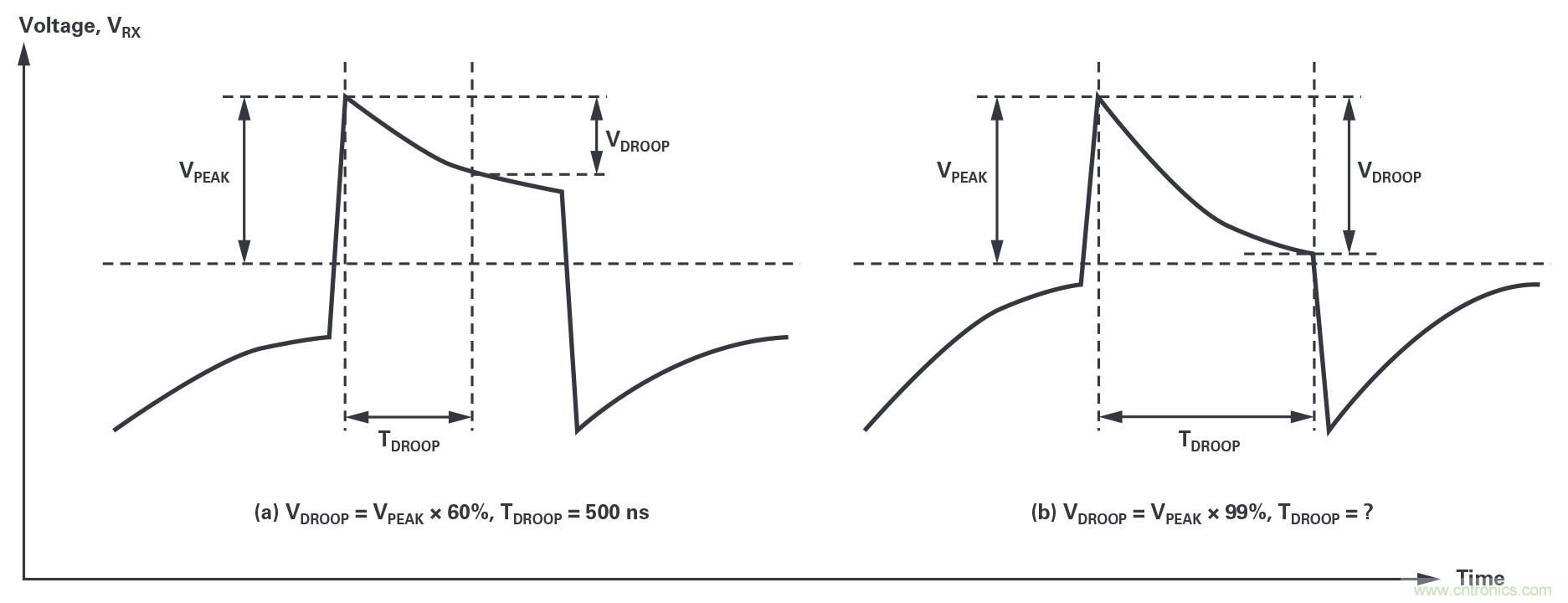

選擇電感(L)和電容(C)值時(shí),需要考慮最大的RS-485/RS-422總線壓降和壓降時(shí)間�����,如圖6所示��。存在一些標(biāo)準(zhǔn)�����,例如對(duì)于單根雙絞線以太網(wǎng)2�����,指出的最大可允許壓降和壓降時(shí)間如圖6a所示。對(duì)于有些系統(tǒng)�����,最大的可允許壓降和壓降時(shí)間值可能更大�����,受信號(hào)極性交越點(diǎn)限制�����,如圖6b所示��。

壓降和壓降時(shí)間可與圖5中的仿真配對(duì)���,以確定系統(tǒng)的高通頻率���。

對(duì)于衰減出色的系統(tǒng),高通濾波器截止頻率和壓降要求之間的關(guān)系如公式1.3所示

在SPI至RS-485/RS-422通信系統(tǒng)中增加虛假電源時(shí)���,很顯然可允許的最低SPI SCLK速率會(huì)受虛假電源濾波器元件限制��。

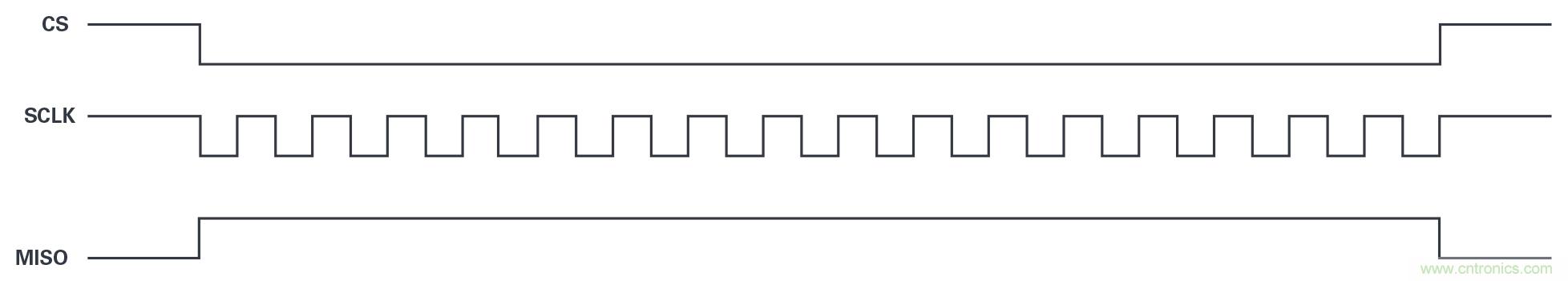

為了實(shí)現(xiàn)不含位錯(cuò)誤的可靠通信���,需要考慮最糟糕場(chǎng)景下的最低SPI SCLK���,例如,當(dāng)所有的SPI MISO采樣位處于邏輯高電平時(shí)�����,如圖7所示��。如果所有的MISO采樣位都處于邏輯高電平��,會(huì)導(dǎo)致位數(shù)據(jù)數(shù)率低于系統(tǒng)SPI SCLK��。例如���,如果SPI SCLK為2 MHz,且所有16個(gè)位都處于邏輯高電平�����,那么虛假電源LC濾波器網(wǎng)絡(luò)的速率相當(dāng)于125 kHz的SPI MISO位數(shù)率��。

如“時(shí)間同步和電纜長(zhǎng)度”部分所示,電纜長(zhǎng)度越長(zhǎng)�����,需要的SPI SCLK速率越低���。但是�����,虛假電源會(huì)限制最低的SPI SCLK速率���。要平衡這些對(duì)立的要求,就需要小心選擇和確定無源濾波器元件的特性���,尤其是電感���。

圖5.RS-422發(fā)射數(shù)據(jù)路徑和RS-485/RS-422接收數(shù)據(jù)路徑的二階高通濾波器。

圖6.RS-422接收器的壓降和壓降時(shí)間�����。

圖7.具有MISO 16位突波(所有都處于邏輯高電平)的SPI協(xié)議���。

無源元件選擇

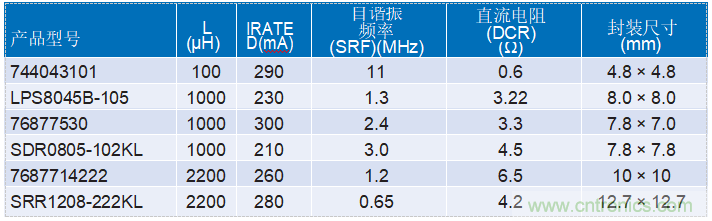

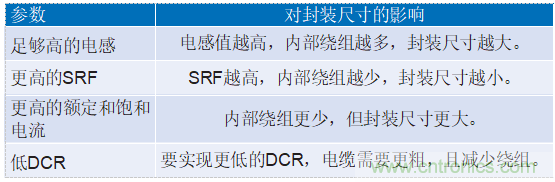

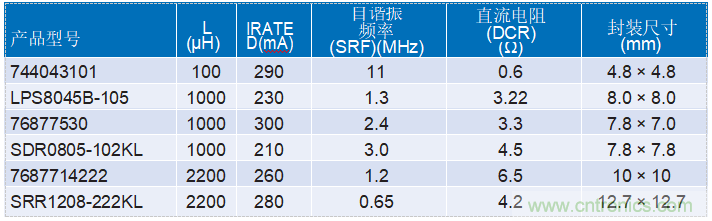

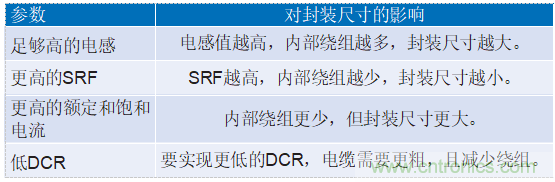

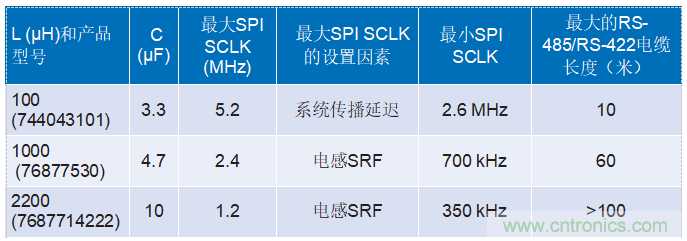

在選擇合適的功率電感時(shí)���,需要考慮許多參數(shù)���,包括足夠的電感、額定/飽和電流�����、自諧振頻率(SRF)��、低直流電阻(DCR)和封裝尺寸��。表1提供選擇的功率電感和參數(shù)��。

額定電流需要滿足或超過遠(yuǎn)程供電的MEMS傳感器節(jié)點(diǎn)的總電流要求�����,額定飽和電流需要更大���。

此電感不會(huì)給交流數(shù)據(jù)造成高于其SRF的高阻抗,在達(dá)到某個(gè)點(diǎn)之后��,會(huì)開始呈現(xiàn)電容性阻抗特性。選擇的電感SRF會(huì)限制在SPI至RS-485/RS-422物理層上使用的最大SPI SCLK��,如圖1所示���。在長(zhǎng)電纜上使用時(shí)��,可能不會(huì)接觸到SRF電感���;例如,電纜超過10米時(shí)��,可能無法達(dá)到11 MHz SPI SCLK速率(產(chǎn)品型號(hào)為744043101的SRF)��。在其他情況下�����,在長(zhǎng)電纜上運(yùn)行時(shí)�����,電感SRF可能達(dá)到更低的SPI SCLK速率(2.4 MHz�����、1.2 MHz)。如前所述�����,在虛假電源濾波器網(wǎng)絡(luò)中使用時(shí)��,電感也會(huì)限制可允許的最低SCLK速率�����。

值更大的電感可以采用12.7 mm × 12.7 mm封裝��,值更小的電感可以采用4.8 mm × 4.8 mm封裝�����。

表2顯示在通過權(quán)衡這些對(duì)立要求��,以最小化電感尺寸時(shí)��,會(huì)因?yàn)槲锢硐拗疲▋?nèi)部繞組)等受到限制���。

表1.選擇的功率電感參數(shù)

表2.功率電感——對(duì)封裝尺寸的限制

選擇合適的直流電壓隔離電容時(shí)��,受限因素包括瞬態(tài)過電壓額定值和直流電壓額定值��。直流電壓額定值需要超過最大的總線電壓偏置值���,具體如圖3所示。電路或連接器短路時(shí)���,電感電流會(huì)失衡�����,會(huì)被端電極阻抗消耗���。出現(xiàn)短路時(shí),需要設(shè)置隔直電容的額定值���,以實(shí)現(xiàn)峰值瞬態(tài)電壓��。例如��,在低功率系統(tǒng)中�����,電感飽和電流約為1 A時(shí)�����,對(duì)應(yīng)的隔直電容額定值至少為直流50 V���。4

系統(tǒng)實(shí)現(xiàn)

設(shè)計(jì)窗口和元件選擇

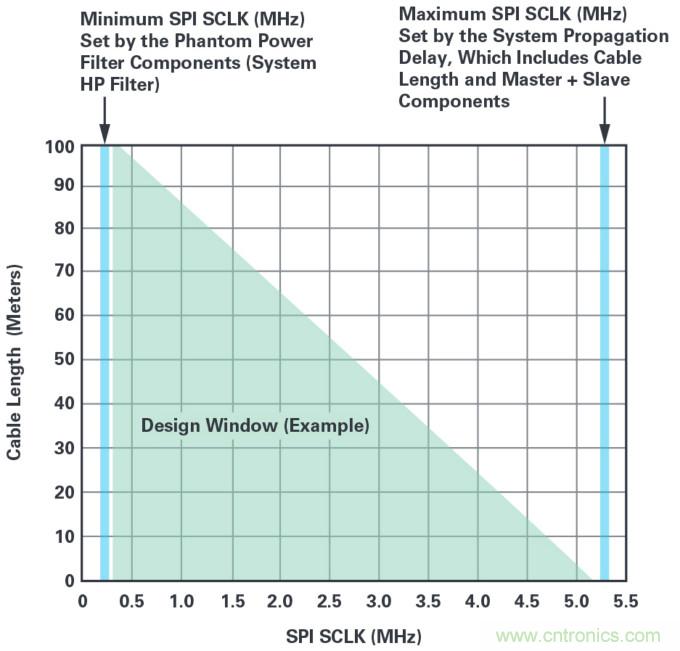

在RS-485/RS-422長(zhǎng)電纜上使用SPI之類的時(shí)鐘同步接口�����,同時(shí)在相同的雙絞線(虛假電源)上部署電源和數(shù)據(jù)時(shí)�����,存在多種設(shè)計(jì)限制��,具體如圖8所示���。可允許的最小SPI SCLK由虛假電源濾波器元件設(shè)置��,即SPI數(shù)據(jù)線上的高通濾波器數(shù)據(jù)��。最大的SPI SCLK由虛假電源電感自諧振頻率(SRF)或系統(tǒng)傳播延遲設(shè)置�����,以SPI SCLK值更低者為準(zhǔn)。

圖8.設(shè)計(jì)窗口限制���。

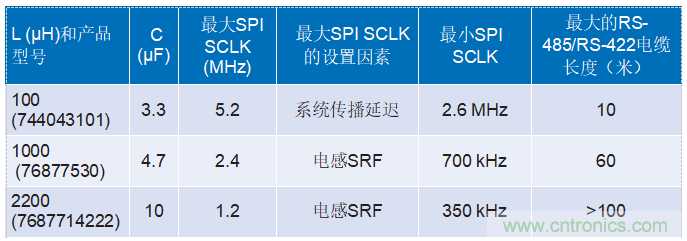

表3提供建議使用的電感和電容值,對(duì)應(yīng)的最小SPI SCLK通過模擬圖5確定��,使用圖6和公式1作為指導(dǎo)���。其中�����,假設(shè)VDROOP為VPEAK的99%��。最小的SPI SCLK也會(huì)考慮最糟糕的場(chǎng)景���,如圖7所示,其中所有數(shù)據(jù)突波位都處于邏輯高電平��。對(duì)應(yīng)的電纜長(zhǎng)度根據(jù)圖2預(yù)估���。最大SPI SCLK由系統(tǒng)傳播延遲或電感SRF值設(shè)置�����。

下面是一個(gè)計(jì)算示例���。

要確定最大SPI SCLK:

● 指明系統(tǒng)所需的電纜長(zhǎng)度��。在本例中��,我們選擇使用10米長(zhǎng)的RS-485/RS-422電纜�����。

● 使用圖2確定系統(tǒng)可允許的最大SPI SCLK��。電纜10米長(zhǎng)時(shí)���,約采用2.6 MHz SPI SCLK。將最大SPI SCLK降低10%���,以獲取LC元件容差���,從而提供2.3 MHz SPI SCLK?����?稍试S的最大SPI SCLK也可能受選擇的電感的SRF限制。

要確定最小SPI SCLK:

● 考慮SPI協(xié)議�����,其中MISO線路上的所有位都處于邏輯高電平���。在本例中,我們選擇使用16位SPI協(xié)議�����,其中會(huì)在32 SCLK瞬態(tài)期間對(duì)16位SPI MISO數(shù)據(jù)采樣��。如果所有16位都處于邏輯高電平�����,那么有效位的速率為2.3 MHz / 32 = 72 kHz�����。

● 按照?qǐng)D5�����,在VTX上的方波為72 kHz時(shí),可以使用多個(gè)L和C值來模擬電纜VRX遠(yuǎn)端上的電壓波形�����。在電纜長(zhǎng)度增加時(shí)�����,電感值和電感封裝尺寸會(huì)增加���。電容值也會(huì)增加��。

● L和C值的選擇可變��,具體由所需的壓降設(shè)置決定�����,如圖6所示�����。在本例中��,假設(shè)VDROOP = VPEAK × 99%�����。

● 在VTX上使用100 µH電感���、3.3 µF電容和72 kHz方波時(shí)�����,會(huì)產(chǎn)生7 µs TDROOP���,其中VDROOP = VPEAK × 99%���。

● 6 µs至7 µs TDROOP相當(dāng)于2.3 MHz至2.6 MHz SPI SCLK���。

● 如果選擇100 µH (744043101)電感,2.6 MHz SPI SCLK低于11 MHz電感SRF���。

如果使用100 µH電感和3.3 µF電容��,可以最大限度減小元件的PCB面積���。使用更大的電感時(shí)�����,例如1000 µH或2200 µH�����,元件的PCB面積可能增大3倍��。最大的SPI SCLK理論值由電感SRF設(shè)置���,這實(shí)際上是不可能的,例如�����,在11 MHz時(shí)在沒有時(shí)鐘補(bǔ)償?shù)南到y(tǒng)中使用100 µH (744043101)�����。

表3.各種虛假電源濾波器元件

如果使用更大的電感��,例如2200 µH,網(wǎng)絡(luò)需要更多電容和電阻來衰減系統(tǒng)諧振���。額外的元件用藍(lán)色表示�����,在圖9中標(biāo)記為RDAMP (1 kΩ)和CDAMP (47 µF)���。

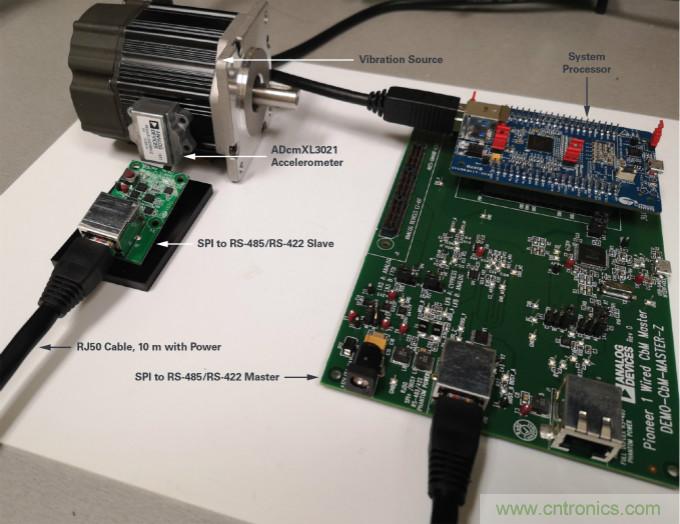

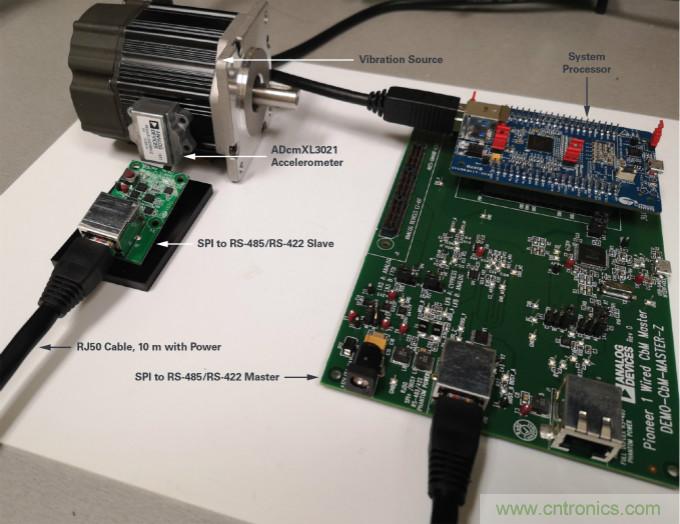

實(shí)驗(yàn)設(shè)置

圖10所示為ADI公司的有線CbM評(píng)估平臺(tái),因此被稱為Pioneer 1��。此系統(tǒng)使用第一部分所示的SPI至RS-485/RS-422設(shè)計(jì)解決方案��。Pioneer 1也包括ADcmXL3021寬帶寬��、低噪聲�����、三軸MEMS加速度計(jì)�����,將高性能和多種信號(hào)處理功能結(jié)合到一起���,以簡(jiǎn)化CbM系統(tǒng)中的智能傳感器節(jié)點(diǎn)開發(fā)��。SPI至RS-485/RS-422從機(jī)將ADcmXL3021 SPI輸出通過10米電纜返回到主機(jī)控制器�����,以實(shí)施振動(dòng)數(shù)據(jù)分析��。SPI至RS-485設(shè)計(jì)使用虛假電源100 µH電感和3.3 µF電容來最小化從機(jī)接口解決方案的尺寸�����,該方案的大小為26 mm × 28 mm(不包括接口連接器)��。

圖9.增加更多系統(tǒng)衰減��,以支持更大的電感和電容濾波器�����。

圖10.Pioneer 1基于狀態(tài)監(jiān)控的有線評(píng)估系統(tǒng)�����。

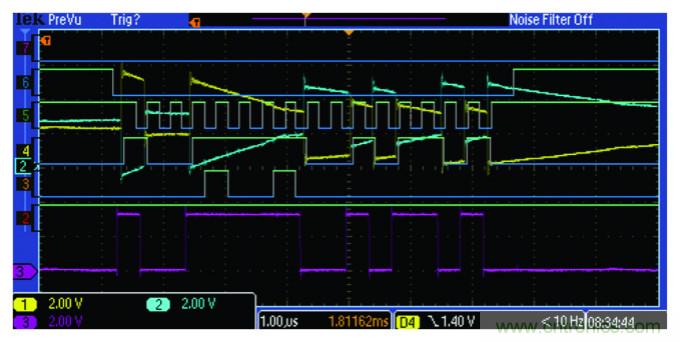

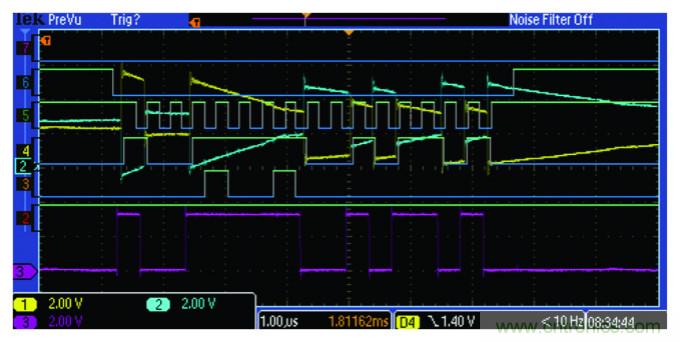

虛假電源線上的交流數(shù)據(jù)波形

圖11和表4顯示在SPI主機(jī)和從機(jī)上�����,以及在RS-485/RS-422差分電壓總線上測(cè)量的電壓���。這些電壓使用圖10中的示例應(yīng)用設(shè)置測(cè)量���。模擬信號(hào)1(黃色)和2(藍(lán)色)是表示MISO信號(hào)(紫色)的總線壓差,在SPI從機(jī)輸出端測(cè)量��。數(shù)字信號(hào)4(黃色)顯示在主機(jī)控制器上采樣的MISO���。SPI主機(jī)上的MISO信號(hào)與SPI從機(jī)上的MISO的極性和相位匹配�����,且無傳播延遲�����。

表4.測(cè)量的示波器通道和信號(hào)

圖11.在SPI主機(jī)和從機(jī)上�����,以及在RS-422差分電壓總線上測(cè)量的電壓。

虛假電源線上的直流正確性

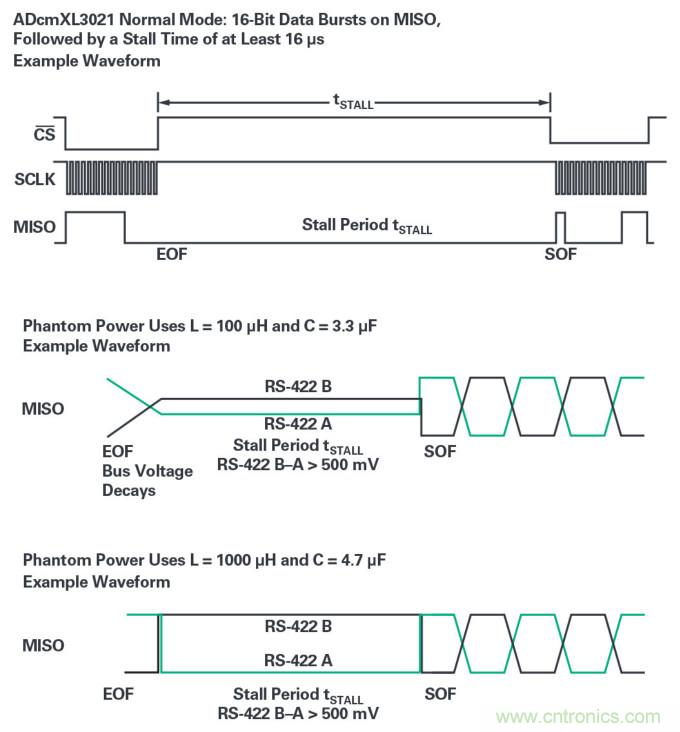

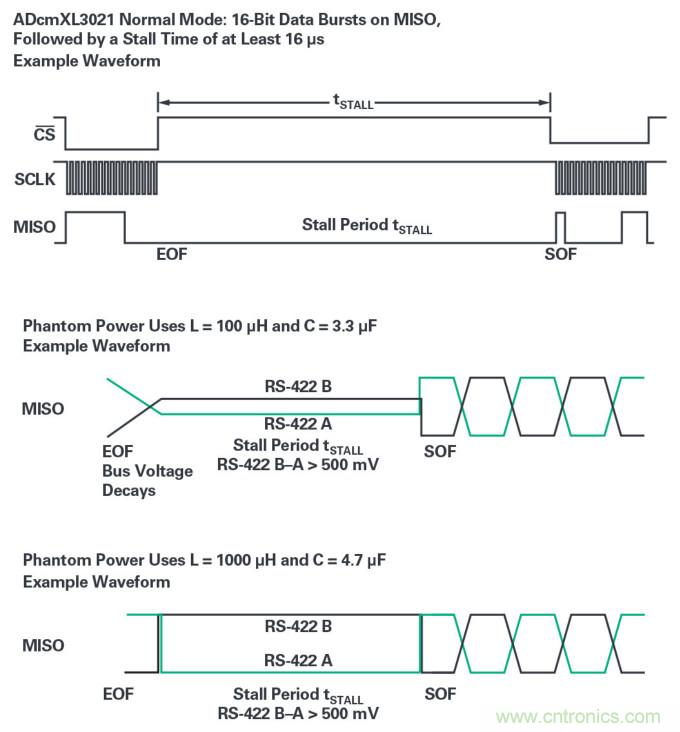

圖12表示ADcmXL3021正常模式,其中包括SPI協(xié)議���,該協(xié)議在MISO上發(fā)送16位數(shù)據(jù)突波��,之后空閑一段時(shí)間(最短16 µs)���,然后再發(fā)送另一個(gè)16位數(shù)據(jù)突波。

在虛假電源網(wǎng)絡(luò)中���,使用100 µH電感和3.3 µF電容:

● 在幀末尾(EOF)�����,RS-485/RS-422總線電壓衰減回到穩(wěn)定的直流狀態(tài)���。

● 空閑期直流穩(wěn)定狀態(tài)要求差分電壓RS-422 B-A > 500 mV,用于反映ADcmXL3021 MISO高阻狀態(tài)�����,以及確保ADM4168E收發(fā)器輸出上提供邏輯0�����。如圖4中的濾波器電路所示,如果使用500 Ω電阻���,即可確保這個(gè)空閑狀態(tài)的正確性���。

● 下一個(gè)幀起始(SOF)將從低電平正確瞬變到高電平,或者保持低電平��,具體由ADcmXL3021的MISO數(shù)據(jù)輸出決定�����。

● 空閑期RS-485/RS-422總線穩(wěn)定狀態(tài)不與SPI SCLK邊緣對(duì)應(yīng)�����,所以隨機(jī)噪聲不會(huì)影響這段時(shí)間內(nèi)的SPI MISO數(shù)據(jù)采樣��。

在虛假電源網(wǎng)絡(luò)中���,使用1000 µH電感和4.7 µF電容:

uADcmXL3021 MISO輸出之后依次出現(xiàn)EOF���、空閑期和SOF,在空閑期���,總線電壓電平不會(huì)衰減回到500 mV最低直流穩(wěn)定狀態(tài)�����?��?赡艹霈F(xiàn)一定的電壓電平衰減,但不會(huì)衰減到500 mV���。

圖12.虛假電源線上的直流正確性��。

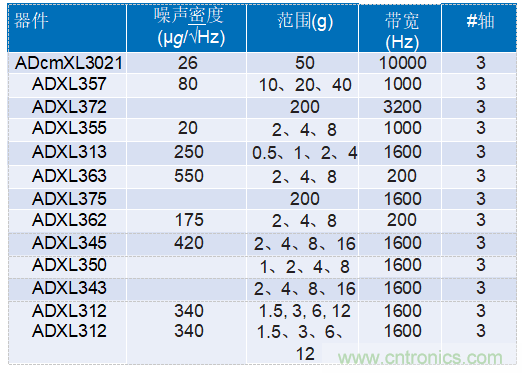

有線評(píng)估解決方案

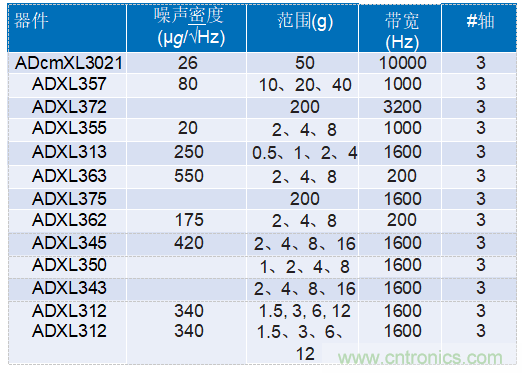

ADI公司開發(fā)出Pioneer 1有線系統(tǒng)評(píng)估解決方案���,以支持ADcmXL3021三軸MEMS加速度計(jì)。如維基百科指南所述���,Pioneer 1評(píng)估套件也可以利用擴(kuò)展板���,支持表5所示的MEMS器件。

表5.適用于MEMS傳感器的有線評(píng)估解決方案

參考資料

1 Richard Anslow和Dara O’Sullivan��。“為工業(yè)4.0啟用可靠的基于狀態(tài)的有線監(jiān)控——第1部分��。”ADI公司,2019年7月�����。

2 “IEEE 802.3bu-2016——IEEE以太網(wǎng)標(biāo)準(zhǔn)——修正案8:?jiǎn)胃胶怆p絞線以太網(wǎng)由數(shù)據(jù)線供電(PoDL)的電線的物理層和管理參數(shù)���。”IEEE���,2017年2月。

3 Andy Gardner��。“PoDL:去耦網(wǎng)絡(luò)演示��。”凌力爾特���,2014年5月���。

4 Andy Gardner。“PoDL瞬時(shí)連接器和電纜短路���。”凌力爾特���,2014年9月��。

作者簡(jiǎn)介

Richard Anslow是ADI公司自動(dòng)化與能源業(yè)務(wù)部互連運(yùn)動(dòng)和機(jī)器人團(tuán)隊(duì)的系統(tǒng)應(yīng)用工程師���。他的專長(zhǎng)領(lǐng)域是基于狀態(tài)的監(jiān)測(cè)和工業(yè)通信設(shè)計(jì)。他擁有愛爾蘭利默里克大學(xué)頒發(fā)的工程學(xué)士學(xué)位和工程碩士學(xué)位���。聯(lián)系方式:richard.anslow@analog.com。

Dara O’Sullivan是ADI公司自動(dòng)化與能源業(yè)務(wù)部互連運(yùn)動(dòng)和機(jī)器人團(tuán)隊(duì)的系統(tǒng)應(yīng)用經(jīng)理��。他的專長(zhǎng)領(lǐng)域是工業(yè)運(yùn)動(dòng)控制應(yīng)用的功率轉(zhuǎn)換��、控制和監(jiān)測(cè)�����。Dara擁有愛爾蘭科克大學(xué)工程學(xué)士���、工程碩士和博士學(xué)位��。自2001年起��,Dara便從事研究�����、咨詢和工業(yè)領(lǐng)域的工業(yè)與可再生能源應(yīng)用方面的工作�����。聯(lián)系方式:dara.osullivan@analog.com

推薦閱讀: