【導(dǎo)讀】芯片設(shè)計中幾個重要的指標總是讓設(shè)計工程師自以為是的想到各種折中的方法,實則不然。在實際電路設(shè)計中,不要僅僅考慮功能實現(xiàn),需要多想想是否有更好的解決方案,讓面積,速度,功耗表現(xiàn)更佳才是上策。當然這也是優(yōu)秀的工程師和平庸的工程師設(shè)計出來的產(chǎn)品會有巨大的差異。

在芯片設(shè)計中,大家通常都會注意到幾個重要的指標:

速度:電路可以跑多少MHz的時鐘頻率,一般來說,速度越快,能處理的數(shù)據(jù)量就越多,性能越好。

面積:電路的物理實現(xiàn)需要占用硅片的面積,占用的面積越小,成本越低。

功耗:電路工作所消耗的能量,功耗越低,芯片越省電,發(fā)熱量 也越低,能耗低,環(huán)保。

書本上說,速度、面積、功耗是互相牽制的,在相同的制造工藝(制程)條件下,一般來說,速度越快,晶體管尺寸越大,面積就越大,功耗也越高。

為了降低功耗,可以降低芯片的工作速度,讓時鐘的跳變頻率變慢。

為了降低成本,減小芯片面積,可以采用面積比較小(W比較小)的晶體管,由于電流和W成正比,因此面積減小,速度會變慢。(為了即減小面積,同時提高速度,則必須讓L變小,也就是提升制程,65nm換成45nm,45nm換成28nm等等)

為了提高速度,我們需要加大充電電流,加大電流,必然導(dǎo)致功耗增加。(為了不增加電流而提高速度,必須減少電容,或者降低充電電壓,這兩個動作也是靠工藝水平的提升來實現(xiàn),比如45nm換成28nm工藝)

請大家注意,上面的速度、面積、功耗的折中和互相牽制是建立在相同制程,相同的IP Vendor,以及相同的電路條件下。我想要提醒的是,如果不滿足這3個條件,這3個因素可能不是折中的關(guān)系,有可能會出現(xiàn)速度慢,面積大,功耗也高的情況。說明如下:

1 )在相同的工藝制程,相同的IP Vendor(包括相同的標準單元)條件下,同一個功能,不同的電路實現(xiàn)方案,有可能會出現(xiàn)方案A比方案B面積大,速度慢,功耗高。舉例說明:

實現(xiàn)一個6分頻電路:

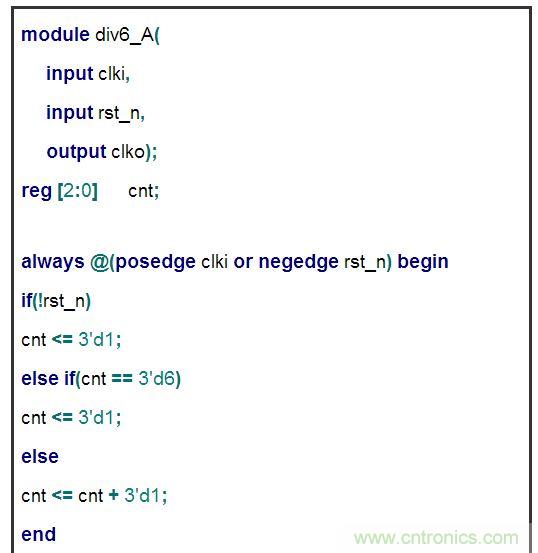

方案A:

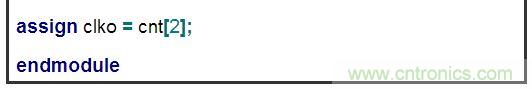

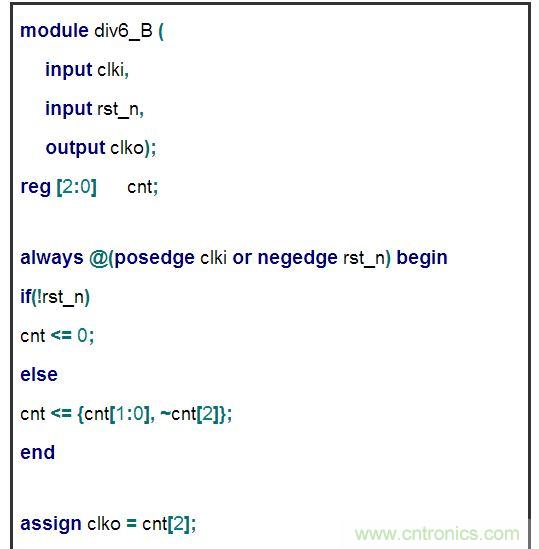

方案B:

上面的電路,功能一模一樣,都實現(xiàn)了時鐘6分頻。方案A的使用了加法, 方案B采用了循環(huán)移位。很明顯,

# 加法比移位的邏輯電路多,方案A的面積比方案B大;

# 加法需要的邏輯路徑長,因此方案A的最快工作頻率低于方案B

# 方案B邏輯少,數(shù)據(jù)變化產(chǎn)生的節(jié)點電壓變化少,并且,方案B類似格雷碼,觸發(fā)器的跳變次數(shù)也比方案A要少,因此方案B的功耗小。

綜上所述,方案A比方案B,面積大,速度慢,功耗高。徹底的完敗。

因此,在實際電路設(shè)計中,不要僅僅考慮功能實現(xiàn),需要多想想是否有更好的解決方案,讓面積,速度,功耗表現(xiàn)更佳;優(yōu)秀的工程師和平庸的工程師設(shè)計出來的產(chǎn)品會有巨大的差異,競爭力體現(xiàn)在人才的智慧上,聰明的大腦在芯片設(shè)計中至關(guān)重要。我們每個設(shè)計工程師都要力爭成為智慧的工程師。

2)同樣的數(shù)字電路,選擇不同的標準單元庫,有可能會出現(xiàn)標準單元庫A的實現(xiàn), 比標準單元庫B的實現(xiàn)面積大,功耗大,速度也慢。可以參考上面的解釋,因為不同的標準單元庫是不同的人設(shè)計出來的,也有聰明和平庸之分。即使同一個 Vendor的不同標準單元庫,也可能會發(fā)現(xiàn)新的改進庫比原來的面積,速度,功耗都要優(yōu)。模擬IP也如此,不同的Vendor有差異。 由于IP 庫的差異,對設(shè)計工程師提出了更多要求,要求芯片設(shè)計者能夠甄別比較優(yōu)秀的IP,從而提升產(chǎn)品的整體競爭力。IP如果選擇了比較平庸的,將來產(chǎn)品的競爭力 就會大打折扣。