【導(dǎo)讀】過采樣和數(shù)字濾波有助于降低對ADC前置的抗混疊濾波器的要求。重構(gòu)DAC可以通過類似的方式運用過采樣和插值原理。例如,數(shù)字音頻CD播放器常常采用過采樣,其中來自CD的基本數(shù)據(jù)更新速率為44.1 kSPS。早期CD播放器使用傳統(tǒng)的二進制DAC,并將“0”插入并行數(shù)據(jù)中,從而將有效更新速率提高到基本吞吐速率的4倍、8倍或16倍。4×、8×或16×數(shù)據(jù)流通過一個數(shù)字插值濾波器,產(chǎn)生額外的數(shù)據(jù)點。高過采樣速率將鏡像頻率移動到更高位置,從而可以使用較為簡單、成本更低、過渡帶更寬的濾波器。此外,由于存在處理增益,信號帶寬內(nèi)的SNR也會提高。Σ-Δ型DAC架構(gòu)使用高得多的過采樣速率,將這一原理擴展到極致,因而在現(xiàn)代CD播放器中頗受歡迎。

同樣的過采樣和插值原理也可用于通信領(lǐng)域的高速DAC,以便降低對輸出濾波器的要求,并利用處理增益提高SNR。

重構(gòu)DAC的輸出頻譜

重構(gòu)DAC的輸出可以表示為一系列矩形脈沖,其寬度等于時鐘速率的倒數(shù),如圖1所示。

圖1:顯示鏡像和sin (x)/x滾降的無濾波DAC輸出

請注意,在奈奎斯特頻率fc/2,重構(gòu)信號幅度降低3.92 dB。如果需要,可以使用一個反sin(x)/x濾波器來補償此效應(yīng)?;ㄐ盘柕溺R像作為采樣函數(shù)的結(jié)果出現(xiàn),并且也通過sin(x)/x函數(shù)衰減。

過采樣插值DAC

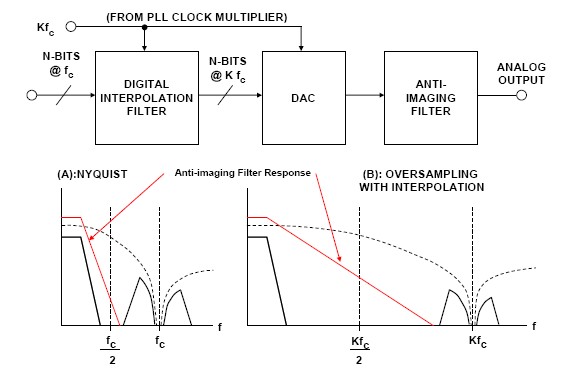

過采樣/插值DAC的基本原理如圖2所示。N位輸入數(shù)據(jù)字以速率fc接收。數(shù)字插值濾波器以等于過采樣頻率Kfc的時鐘速率工作,并插入額外的數(shù)據(jù)點。對輸出頻譜的影響如圖2所示。在奈奎斯特采樣頻率下(A),對模擬抗鏡像濾波器的要求可能相當(dāng)高。通過過采樣和插值,可以大大降低對該濾波器的要求,如(B)所示。此外,量化噪聲分布在比原始信號帶寬更寬的區(qū)域內(nèi),因而信噪比也會有所提高。原始采樣速率加倍時(K = 2),SNR提高3 dB;K = 4時,SNR提高6 dB。早期CD播放器利用了這一點,一般能將數(shù)字濾波器中的算法精確到N位以上。如今,CD播放器中的多數(shù)DAC都是Σ-Δ型。

關(guān)于過采樣/插值DAC原理的最早期文獻有Ritchie、Candy和Ninke于1974發(fā)表的論文(參考文獻1),以及Mussman和Korte于1981年(申請日期)申請的專利(參考文獻2)。

圖2:過采樣插值DAC

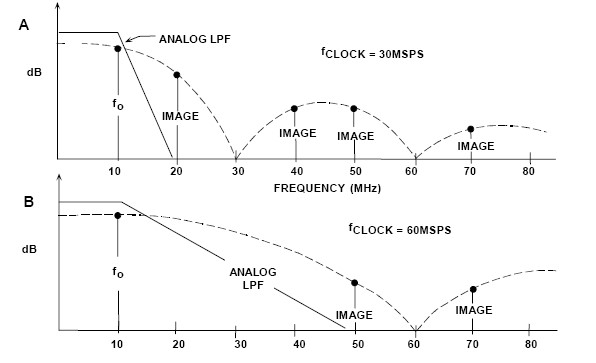

下例使用一些實際的數(shù)值來說明過采樣原理。假設(shè)以30 MSPS的輸入字速率驅(qū)動一個傳統(tǒng)DAC(參見圖3A),DAC輸出頻率為10 MHz。在30 – 10 = 20 MHz時的鏡像頻率成分必須通過模擬抗混疊濾波器進行衰減,濾波器的過渡帶始于10 MHz,止于20 MHz。假設(shè)必須將鏡像頻率衰減60 dB,則在10 MHz到20 MHz(一個倍頻程)的過渡帶內(nèi),濾波器必須從10 MHz的通帶轉(zhuǎn)折頻率變?yōu)?0 dB的阻帶衰減。濾波器每個極點提供大約6 dB/倍頻程的衰減。因此,為了提供所需的衰減,至少需要10個極點。過渡帶越窄,則濾波器越復(fù)雜。

圖3:fo = 10 MHz時的模擬濾波器要求:(A) fc = 30 MSPS,(B) fc = 60 MSPS

假設(shè)我們將DAC更新速率提高到60 MSPS,并在各原始數(shù)據(jù)采樣點之間插入“0”?,F(xiàn)在,并行數(shù)據(jù)流為60 MSPS,但我們必須確定零值數(shù)據(jù)點的值,這通過將添加0的60 MSPS數(shù)據(jù)流經(jīng)由數(shù)字插值濾波器處理來實現(xiàn),由濾波器計算額外的數(shù)據(jù)點。2× 過采樣頻率下的數(shù)字濾波器響應(yīng)曲線如圖3B所示。模擬抗混疊濾波器過渡區(qū)現(xiàn)在是10 MHz到50 MHz(第一鏡像出現(xiàn)在2fc – fo = 60 – 10 = 50 MHz)。該過渡區(qū)稍大于2個倍頻程,說明5或6極點濾波器即足夠。

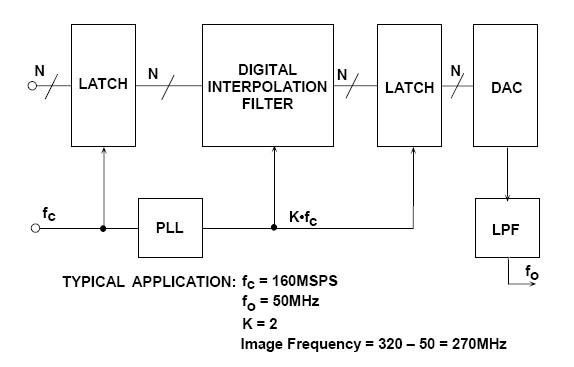

AD9773/AD9775/AD9777(12-/14-/16-bit)系列發(fā)射DAC (TxDAC®)是2×、4×或8×可選過采樣插值雙通道DAC,圖4為其簡化框圖。這些器件能夠處理最高達160 MSPS的12/14/16位輸入字速率,最大輸出字速率為400 MSPS。假設(shè)輸出頻率為50 MHz,輸入更新速率為160 MHz,過采樣比為2,則鏡像頻率出現(xiàn)在320 MHz – 50 MHz = 270 MHz,因此模擬濾波器的過渡帶為50 MHz至270 MHz。如果沒有2倍過采樣,則鏡像頻率出現(xiàn)在160 MHz – 50 MHz = 110 MHz,濾波器過渡帶為50 MHz至110 MHz。

圖4:過采樣插值TxDAC®的簡化框圖

還應(yīng)注意,過采樣插值DAC支持較低的輸入時鐘頻率和輸入數(shù)據(jù)速率,因而它在系統(tǒng)內(nèi)產(chǎn)生噪聲的可能性要低得多。

Σ-Δ型DAC

Σ-Δ型DAC的工作原理與Σ-Δ型ADC非常相似,但在Σ-Δ型DAC中,噪聲整形功能是利用數(shù)字調(diào)制器實現(xiàn)的,而不是利用模擬調(diào)制器。

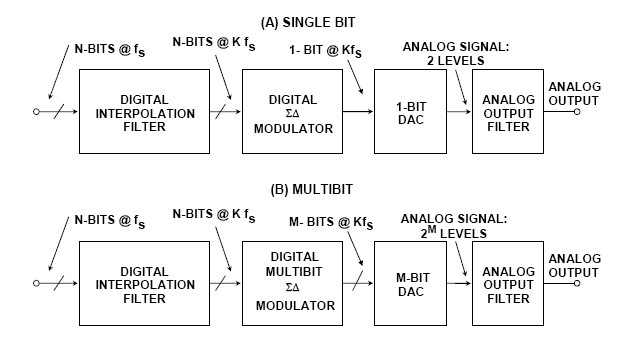

與Σ-Δ型ADC不同,Σ-Δ型DAC大多是數(shù)字式(參見圖5A)。它由一個“插值濾波器”(一個數(shù)字電路,以低速率接受數(shù)據(jù),以高速率插入0,然后應(yīng)用數(shù)字濾波器算法并以高速率輸出數(shù)據(jù))、一個Σ-Δ型調(diào)制器(它對信號是低通濾波器,對量化噪聲則是高通濾波器,并將由此產(chǎn)生的數(shù)據(jù)轉(zhuǎn)換為高速位流)和一個1位DAC組成,該DAC的輸出在等值正負基準(zhǔn)電壓之間切換。輸出在外部模擬低通濾波器(LPF)中濾波。由于過采樣頻率很高,該LPF的復(fù)雜度遠低于傳統(tǒng)奈奎斯特采樣頻率下的情況。

圖5:Σ-Δ型DAC

Σ-Δ型DAC可以使用多位,這就是圖5B所示的“多位”架構(gòu),其原理與之前討論的插值DAC相似,不過增加了Σ-Δ型數(shù)字調(diào)制器。

過去,由于n位內(nèi)部DAC的精度要求(它雖然只有n位,但必須具有最終位數(shù)N位的線性度),多位DAC難以設(shè)計。然而,AD195x系列音頻DAC利用專有“數(shù)據(jù)加擾”技術(shù)(稱為“數(shù)據(jù)定向加擾”)解決了這一問題,在所有音頻規(guī)格方面都能提供出色的性能。

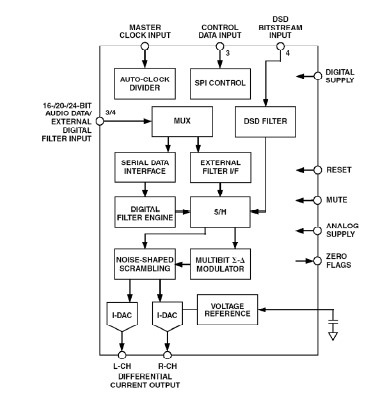

圖6所示為AD1955 多位Σ-Δ型音頻DAC。 AD1955同樣使用數(shù)據(jù)定向加擾技術(shù),支持各種DVD音頻格式,并具有非常靈活的串行端口。THD + N典型值為110 dB。

圖6:AD1955多位Σ-Δ型音頻DAC

總結(jié)

在現(xiàn)代數(shù)據(jù)采樣系統(tǒng)中,過采樣結(jié)合數(shù)字濾波是強有力的工具。我們已經(jīng)看到,同樣的基本原理既適用于ADC,也適用于重構(gòu)DAC。主要優(yōu)點是對抗混疊/抗鏡像濾波器的要求得以降低,另一個優(yōu)點是SNR因處理增益而提高。

Σ-Δ型ADC和DAC架構(gòu)是過采樣原理的終端擴展,同時也是大多數(shù)語音頻帶和音頻信號處理數(shù)據(jù)轉(zhuǎn)換器應(yīng)用的首選架構(gòu)。

參考文獻

1. G. R. Ritchie, J. C. Candy, and W. H. Ninke, "Interpolative Digital-to-Analog Converters," IEEE Transactions on Communications, Vol. COM-22, November 1974, pp. 1797-1806.(最早的關(guān)于過采樣插值DAC的論文之一)。

2. H. G. Musmann and W. W. Korte, "Generalized Interpolative Method for Digital/Analog Conversion of PCM Signals," U.S. Patent 4,467,316, filed June 3, 1981, issued August 21, 1984.(關(guān)于插值DAC的描述)。

3. Robert W. Adams and Tom W. Kwan, "Data-directed Scrambler for Multi-bit Noise-shaping D/A Converters," U.S. Patent 5,404,142, filed August 5, 1993, issued April 4, 1995.(描述采用“數(shù)據(jù)加擾”技術(shù)的分段音頻DAC)。

4. Y. Matsuya, et. al., "A 16-Bit Oversampling A/D Conversion Technology Using Triple-Integration Noise Shaping," IEEE Journal of Solid-State Circuits, Vol. SC-22, No. 6, December 1987, pp. 921-929.

5. Y. Matsuya, et. al., "A 17-Bit Oversampling D/A Conversion Technology Using Multistage Noise Shaping," IEEE Journal of Solid-State Circuits, Vol. 24, No. 4, August 1989, pp. 969-975.

6. Walt Kester, Analog-Digital Conversion, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 3.另見The Data Conversion Handbook, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 3.

© 2009 Analog Devices, Inc 保留所有權(quán)利。對于客戶產(chǎn)品設(shè)計、客戶產(chǎn)品的使用或應(yīng)用,以及因ADI公司協(xié)助而可能導(dǎo)致的任何侵權(quán),ADI公司概不負責(zé)。所有商標(biāo)和標(biāo)志均屬各自所有人所有。ADI公司應(yīng)用與開發(fā)工具工程師提供的信息準(zhǔn)確可靠,但ADI公司對其技術(shù)指南所提供內(nèi)容的技術(shù)準(zhǔn)確性和時效性不承擔(dān)責(zé)任。

推薦閱讀: