【導讀】新興的PLL + VCO (集成電壓控制振蕩器的鎖相環(huán))技術能夠針對蜂窩/4G、微波無線電軍事等應用快速開發(fā)低相位噪聲頻率合成器,ADI集成頻綜產品的頻率覆蓋為25 MHz到13.6 GHz。

蜂窩/4G、微波無線電、測試設備和軍事子系統(tǒng)應用的無線電設計人員依賴高質量本振(LO)來實現低BER(誤碼率)、低雜散輸出和低相位噪聲的系統(tǒng)級目標。所有的RF和微波通信和傳感器系統(tǒng),無論是基于模擬還是數字調制,都需要干凈的LO信號源;無線電的容量越高,對LO信號的要求就越高。有許多不同架構可用,但 產生穩(wěn)定LO源的最常用方法之一是將低相位噪聲電壓控制振蕩器(VCO)和穩(wěn)定基準電壓及鎖相環(huán)(PLL)組合構成頻率合成器。不過,尋求最佳LO性能的設計人員必然會面臨PLL/頻率合成器、VCO、電荷泵及環(huán)路濾波器之間交互的諸多相關挑戰(zhàn),更不用說由于電路板布局和不良電源噪聲所帶來的問題。

ADI的核心專長是在頻率生成元件方面,例如MMIC VCO、鎖相振蕩器(PLO)、低噪聲預分頻器、鑒頻鑒相器(PFD)和一系列RF輸入頻率達13.6 GHz的雙模式(小數/整數)PLL/頻率合成器IC。

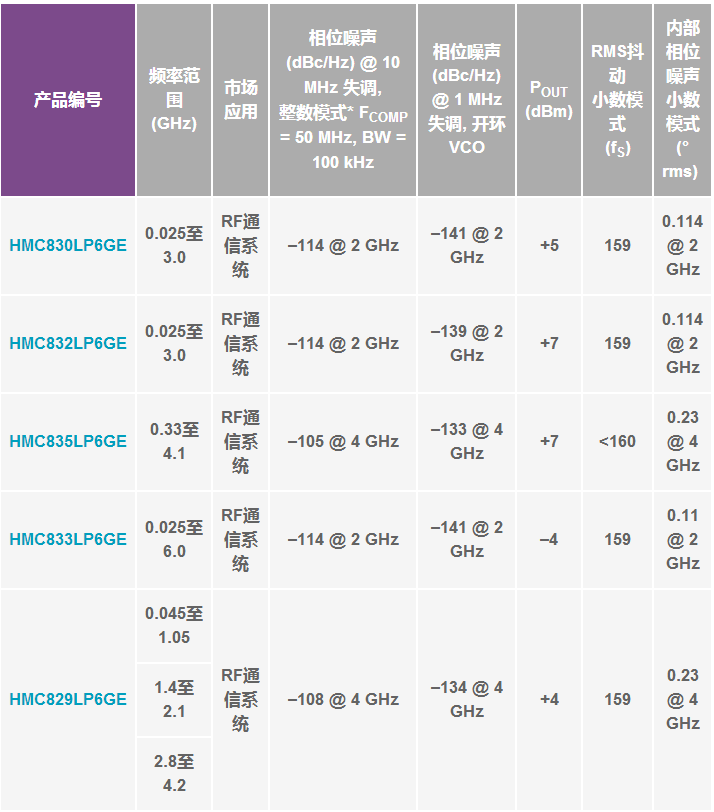

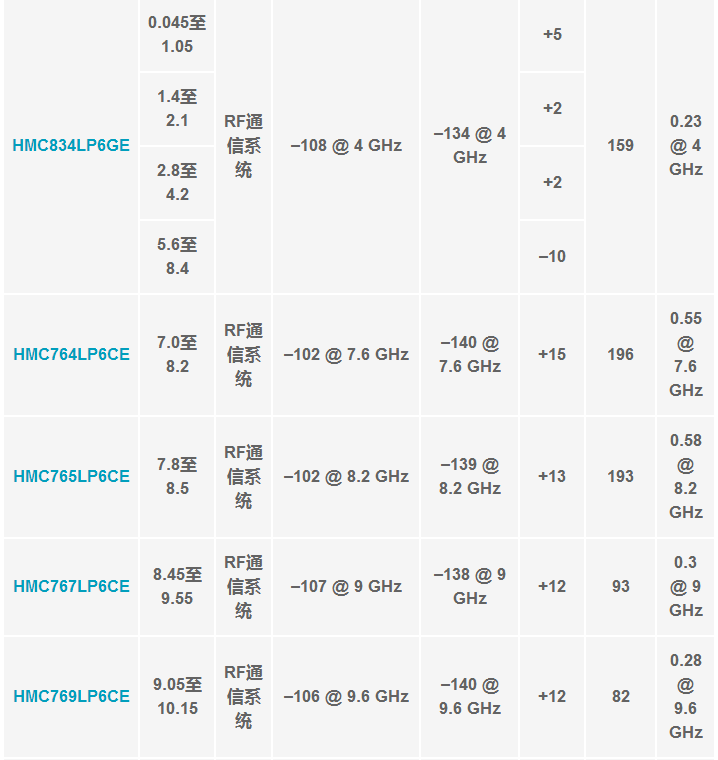

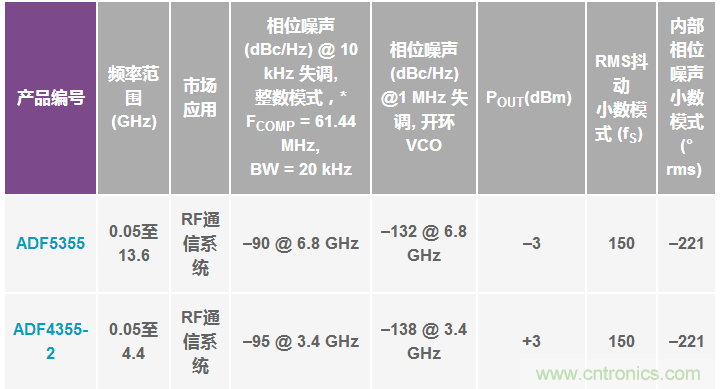

表1和2中列出了業(yè)界領先的ADI集成VCO的PLL產品。這些集成VCO的PLL產品涵蓋從25 MHz到13.6 GHz的RF和微波頻率。

表1. ADI公司集成VCO的PLL性能總結

表2. ADI公司集成VCO的PLL性能總結

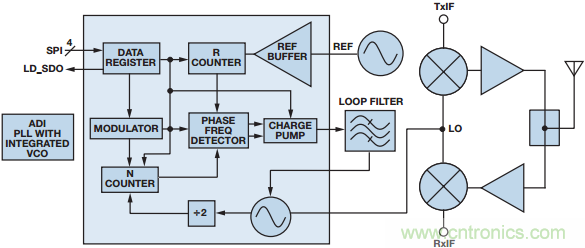

如圖1的功能框圖所示,這些產品采用標準5 mm × 5 mm和6 mm × 6 mm QFN塑料封裝實現了高級小數-N頻率合成器和超低噪聲VCO;這種高水平的集成最大程度地減少了外部元件數。設計針對超低相位噪聲商業(yè)和軍事應用,包括一個極低噪聲鑒頻鑒相器(PFD)、一個精密控制電荷泵和一個提供超精細頻率步進的高 級調制器設計。

圖1. ADI集成VCO的PLL產品功能框圖和典型應用電路

架構具有超低近載波相位噪聲和低雜散,可實現較寬環(huán)路帶寬以及更快的跳頻和低顫噪;雜散輸出足夠低,因此在許多應用中不再需要價格昂貴的直接數字頻率合成(DDS)基準參考源。

適合RF市場應用的集成VCO的PLL

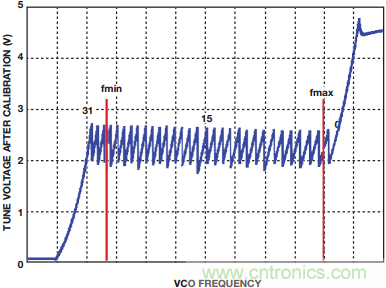

HMC830LP6GE是面向蜂窩/4G、微波回程IF以及測試和測量應用的八個集成VCO寬帶PLL產品之一。該系列的每一個產品都組合了高性能小數-N PLL/頻率合成器和低噪聲VCO。適合RF應用的集成VCO的PLL架構使得高性能VCO可實現五伏以下電壓調諧(參見圖2)。環(huán)路濾波器中不再需要運算放大器,節(jié)省了成本和電路板空間,同 時改善了性能。集成VCO的PLL可以在一個極限溫度下鎖定,之后無需重新鎖定或重新校準即可在整個溫度范圍內工作;該功能是高可靠性應用中所需要的,但是在有些其他競爭對手中并未提供該功能。

圖2. 集成VCO的PLL HMC830LP6GE的調諧電壓與頻率的關系

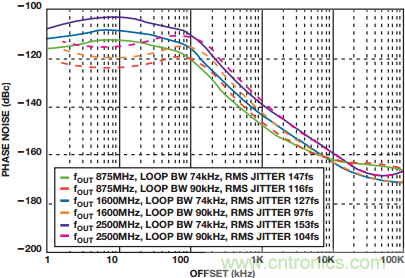

如圖3所示,這些器件具有出色的相位噪聲性能,無論就帶內還是遠端噪底通常都優(yōu)于競爭對手10 dB,而且全部無需在低雜散或低噪聲模式間進行選擇。100 Hz至1 MHz范圍內的集成噪聲通常為–55 dBc,等效于0.1°的rms抖動,或者FOUT = 1 GHz時278 fs rms。

圖3. 集成VCO的PLL HMC830LP6GE的SSB相位噪聲與偏移頻率的關系

如圖4所示,HMC830LP6GE與替代集成解決方案相比有明顯改善。

圖4. 最差雜散,固定50 Mhz基準,輸出頻率= 2 GHz

HMC830LP6GE頻帶邊沿處的溫度范圍性能穩(wěn)定,確保不會出現“壓差”。

例如,HMC830LP6GE在大于20 MHz的偏移頻率下產生大約5 dB近載波相位噪聲和7 dB相位噪底,與TI LMX2581相比,這兩個值都比較低。此外,HMC830LP6GE還提供優(yōu)越的雜散性能,在整個頻段的小數雜散低很多,整個頻譜輸出更干凈。

ADF5355集成VCO的PLL涵蓋同類最寬的頻譜55 MHz至13.6 GHz,而ADF4355-2的頻率范圍是55 MHz至4.4 GHz。兩款器件都集成了超低相位噪聲VCO,對于ADF4355-2而言在3.4 GHz下產生–138 dBc/Hz(1 MHz失調)相位噪聲,而ADF5355在6.8 GHz下產生–132 dBc/Hz(1 MHz失調)相位噪聲。

ADF5355和ADF4355-2采用新型VCO拓撲和架構,并在開發(fā)過程中利用ADI新近獲得專利的先進SiGe-BiCMOS工藝,因而具有出色的VCO相位噪聲性能。在超寬帶寬RF和微波通信應用中,該超低相位噪聲具有改善整體系統(tǒng)誤碼率并提升數據吞吐速率的優(yōu)勢,可提供更佳的抗噪能力和更寬的動態(tài)范圍。

ADI最新的高性價比、超寬帶寬PLL頻率合成器IC還具有高達125 MHz相位比較器頻率和38位分辨率,可降低抖動并允許極為精細的步進大小,而相比分立式GaAs部署方案,采用高級BiCMOS工藝的集成式PLL和VCO可大幅降低封裝尺寸和功耗。另外,由于單個PLL頻率合成器的工作頻率可在55 MHz至13.6 GHz范圍內配 置,因此設計人員可更為快速地對他們的系統(tǒng)設計進行重新配置,并減少器件庫存,同時依然支持多頻段。

適合微波市場應用的集成VCO的PLL

集成VCO的PLL HMC764LP6CE已針對窄帶、高性能的微波通信應用進行了優(yōu)化。ADI公司在業(yè)界率先推出頻率高于6 GHz的集成PLL和VCO。這些產品除了提供ADI出色的微波VCO性能之外,還增加了集成式高級小數頻率合成器的功能。典型應用包括微波和毫米波無線電、工業(yè)/醫(yī)療測試設備、軍事通信、電子戰(zhàn)(EW)和電子對抗 (ECM)子系統(tǒng)。

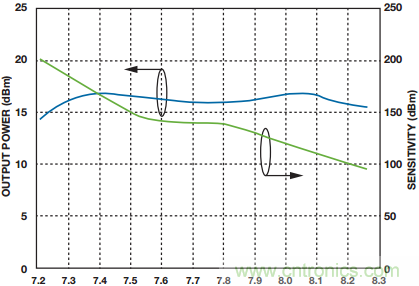

如圖5所示,HMC764LP6CE在其帶寬內具有穩(wěn)定的調諧敏感度和高達16 dBm的輸出功率,因而非常適合直接驅動許多ADI高線性度、雙平衡和I/Q混頻器以及上變頻和下變頻產品的LO部分。

圖5. 集成VCO的PLL HMC764LP6CE的調諧靈敏度和RF輸出功率與輸出頻率的關系

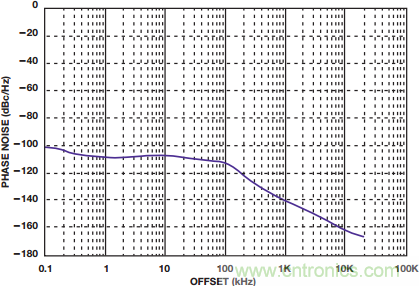

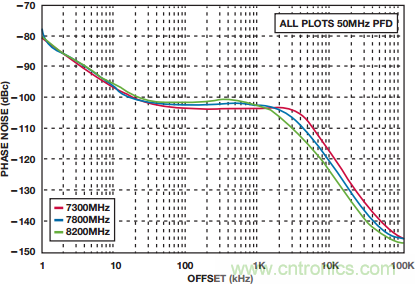

圖6顯示,對于低、中和高頻范圍,HMC764LP6CE卓越的單邊帶(SSB)相位噪聲性能與偏移頻率的關系。測量該數據時參考頻率為50 MHz,環(huán)路帶寬為100 kHz,而且PFD的比較頻率為50 MHz。由于采用單芯片結構,在溫度范圍內及機械沖擊條件下,相位噪聲性能也很穩(wěn)定。此外,內置FSK模式使得器件可用作簡單的低成本直接FM發(fā)射源。

圖6. 集成VCO的PLL HMC764LP6CE的SSB相位噪聲與偏移頻率的關系

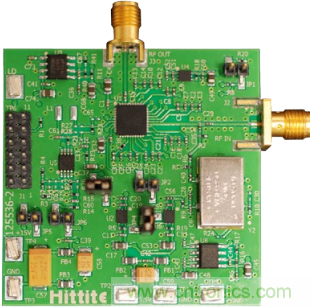

即使具有這樣的高級功能和高集成度,開發(fā)高性能可編程本振仍需要大量設計時間。因此,ADI開發(fā)出集成VCO的PLL參考設計人員套件,從而可以立即測量手頭設計。

圖7所示典型評估PCB是簡單易用的通用評估套件的一部分,它可以最大程度縮短設計時間,便于快速進行原型開發(fā)。參考設計人員套件包括一個板載參考振蕩器和若干穩(wěn)壓器,且支持通用環(huán)路濾波器配置。利用附帶的軟件,用戶可以進行PLL編程以及訪問其高級功能。完整操作指南提供逐步說明,方便用戶完成快速上 電并初始化評估板。本指南全面論述了評估板內使用的元件,涵蓋針對外部基準電壓重新配置評估板,以及實施板載可選擇順序無源或有源環(huán)路濾波器等主題。

圖7. 集成VCO的PLL評估PCB,包含在各設計人員套件中

各個參考設計人員套件均包含ADI專有的ADIsimPLL設計工具,用戶可以根據自己的特定應用定制標準評估PCB環(huán)路濾波器。提供全面的基于PC的PLL控制軟件,可以經由USB接口用PC兼容寄存器文件對PLL進行編程。用戶僅用一臺PC、一臺信號分析儀及若干直流電源,即可在非常短的時間內對完全鎖定的本振進行評估。ADI 公司技術熟練的應用工程師團隊也可幫助客戶快速熟悉這款獨特的產品。

ADI集成VCO的PLL產品將低相位噪聲、高級功能及超小尺寸組合在一起,是微波/毫米波無線電、測試設備、微波傳感器、光纖通信以及軍事通信和傳感器等許多小尺寸應用的理想之選。

混合型頻率合成器通常采用玻璃纖維基板材料,具有一個分立式VCO、一個大型諧振器和一個金屬沖壓蓋。該裝配技術會在用戶系統(tǒng)中造成和RF接地有關的問題,還會產生令人討厭的電氣和顫噪耦合效應。與分立式混合型頻率合成器/VCO配置相比,ADI集成式頻率 生成解決方案有助于設計人員實現穩(wěn)定性能、高可靠性及小尺寸的目標。與大型混合設計相比,ADI集成VCO的PLL的諧振器也小很多,因而具有出色的顫噪性能。這些集成VCO的PLL產品采用符合RoHS標準的QFN無引腳封裝,非常適合高速大批量SMT裝配線。

推薦閱讀: