【導(dǎo)讀】為使高速模數(shù)轉(zhuǎn)換器發(fā)揮 性能��,必須為其提供干凈的直流電源�����。高噪聲電源會(huì)導(dǎo)致信噪比(SNR)下降和/或ADC輸出中出現(xiàn)不良的雜散成分�����。本文將介紹有關(guān)ADC電源域和靈敏度的背景知識(shí)�����,并討論為高速ADC供電的基本原則����。

模擬電源和數(shù)字電源

當(dāng)今的大部分高速模數(shù)轉(zhuǎn)換器至少都有兩個(gè)電源域:模擬電源(AVDD)和數(shù)字與輸出驅(qū)動(dòng)器電源(DRVDD)。一些轉(zhuǎn)換器還有一個(gè)附加模擬電源�����,通常應(yīng)作為本文所討論的額外AVDD電源來(lái)處理�����。轉(zhuǎn)換器的模擬電源和數(shù)字電源是分離的����,以防數(shù)字開(kāi)關(guān)噪聲(特別是輸出驅(qū)動(dòng)器產(chǎn)生的噪聲)干擾器件模擬端的模擬采樣和處理。根據(jù)采樣信號(hào)的不同����,此數(shù)字輸出開(kāi)關(guān)噪聲可能包含顯著的頻率成分,如果此噪聲返回器件的模擬或時(shí)鐘輸入端��,或者通過(guò)電源返回芯片的模擬端,則噪聲和雜散性能會(huì)很容易受其影響而降低��。

對(duì)于大多數(shù)高速模數(shù)轉(zhuǎn)換器��,建議將兩個(gè)獨(dú)立的電源分別用于AVDD和DRVDD�����。這兩個(gè)電源之間應(yīng)有充分的隔離��,防止DRVDD電源的任何數(shù)字開(kāi)關(guān)噪聲到達(dá)轉(zhuǎn)換器的AVDD電源�����。AVDD和DRVDD電源常常采用各自的調(diào)節(jié)器��,然而����,如果在這兩個(gè)電源之間實(shí)現(xiàn)了充分的濾波�����,則采用一個(gè)調(diào)節(jié)器通常也能獲得足夠好的性能�����。

ADC電源靈敏度——PSRR

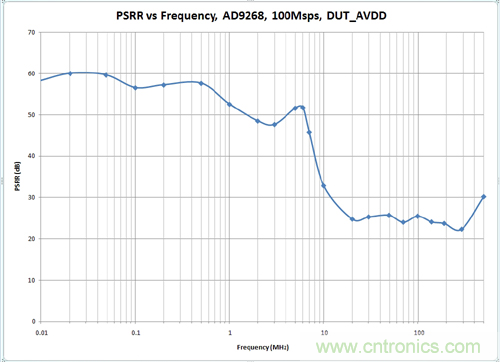

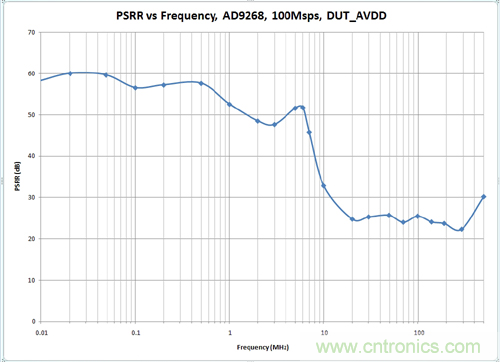

確定高速ADC對(duì)電源噪聲的靈敏度的一個(gè)方法,是將一個(gè)已知頻率施加于轉(zhuǎn)換器的電源軌����,并測(cè)量轉(zhuǎn)換器輸出頻譜中出現(xiàn)的信號(hào)音,從而考察其電源抑制性能����。輸入信號(hào)與輸出頻譜中出現(xiàn)的信號(hào)的相對(duì)功率即為轉(zhuǎn)換器在給定頻率下的電源抑制比(PSRR)。下圖顯示了典型高速ADC的PSRR與頻率的關(guān)系��。此圖中數(shù)據(jù)的測(cè)量條件是將器件安裝于配有旁路電容的評(píng)估板上��,這種方法能夠顯示典型應(yīng)用中器件如何響應(yīng)電源噪聲��。注意在這種情況下�����,轉(zhuǎn)換器的PSRR在低頻時(shí)相對(duì)高得多�����,當(dāng)頻率高于約10MHz時(shí)會(huì)顯著下降。

利用此PSRR信息��,設(shè)計(jì)人員可以確定為了防止噪聲損害轉(zhuǎn)換器的性能����,電源所容許的紋波水平。例如�����,如果一個(gè)電源在500kHz時(shí)具有5mVp-p的紋波����,則從下面的PSRR圖可知,轉(zhuǎn)換器在此頻率提供大約58dB的抑制��。轉(zhuǎn)換器的滿量程為2Vp-p����,因此原始5mV信號(hào)比輸入滿量程低52dB。此信號(hào)將進(jìn)一步衰減58dB�����,從而比轉(zhuǎn)換器的滿量程功率低110dB����。這樣,設(shè)計(jì)人員就能使用轉(zhuǎn)換器的PSRR數(shù)據(jù)來(lái)確定在給定頻率下轉(zhuǎn)換器電源的容許紋波�����。如果轉(zhuǎn)換器的電源在已知頻率具有紋波��,例如來(lái)自上游開(kāi)關(guān)轉(zhuǎn)換器��,則可以利用該方法確定將此噪聲衰減至容許水平所需的額外濾波����。

上述分析假設(shè)給定電源上僅出現(xiàn)一個(gè)頻率。事實(shí)上��,根據(jù)電源獲得方式的不同以及該電源供電對(duì)象的不同��,電源上的噪聲可能具有額外頻率成分��。如果是這種情況��,設(shè)計(jì)人員必須確保為電源提供充分的濾波來(lái)衰減此噪聲��。請(qǐng)注意�����,由于ADC輸入的寬帶特性,在其它奈奎斯特頻率區(qū)中����,處在ADC輸入的目標(biāo)頻帶之外的噪聲可能會(huì)進(jìn)入目標(biāo)頻帶。

關(guān)于線性調(diào)節(jié)器的討論

傳統(tǒng)上使用線性調(diào)節(jié)器來(lái)為轉(zhuǎn)換器的AVDD和DRVDD軌提供干凈的電源��。低壓差線性調(diào)節(jié)器能夠出色地抑制約1MHz以下的低頻噪聲�����。典型LDO的控制環(huán)路帶寬不超過(guò)此頻率����,因此更高頻率的噪聲會(huì)幾乎毫無(wú)衰減地通過(guò)調(diào)節(jié)器。對(duì)于此頻率以上的噪聲�����,必須在LDO之后通過(guò)額外濾波對(duì)其進(jìn)行衰減����,防止此噪聲到達(dá)ADC。通常�����,結(jié)合使用鐵氧體磁珠����、大去耦電容和局部電源去耦,即足以衰減任何通過(guò)線性調(diào)節(jié)器的高頻噪聲�����。設(shè)計(jì)電源濾波器時(shí)必須注意����,如果使用串聯(lián)感性元件,應(yīng)確保上電和掉電時(shí)的感應(yīng)電勢(shì)不會(huì)達(dá)到足以損壞轉(zhuǎn)換器的水平����。

圖1:典型ADC電源抑制比與頻率的關(guān)系

此外,鑒于LDO的上游常常還會(huì)有一個(gè)開(kāi)關(guān)轉(zhuǎn)換器�����,設(shè)計(jì)人員必須確保LDO和濾波器電路能夠充分抑制此開(kāi)關(guān)轉(zhuǎn)換器的頻率?����,F(xiàn)代開(kāi)關(guān)轉(zhuǎn)換器的開(kāi)關(guān)頻率越來(lái)越高,可能高于典型LDO的環(huán)路帶寬����。來(lái)自這些高頻開(kāi)關(guān)轉(zhuǎn)換器的噪聲很容易通過(guò)LDO,必須利用下游濾波器對(duì)其進(jìn)行衰減��。

雖然線性調(diào)節(jié)器能夠很好地為ADC提供干凈的電源��,但效率不高是其主要缺點(diǎn)�����。根據(jù)提供給線性調(diào)節(jié)器輸入端的電壓的不同����,LDO的效率可能非常低。提供一個(gè)略高于LDO壓差的電壓雖然可以提高效率��,但這經(jīng)常需要增加額外的電源級(jí)����,導(dǎo)致電源設(shè)計(jì)的成本和復(fù)雜度隨之增加。

關(guān)于開(kāi)關(guān)調(diào)節(jié)器的討論

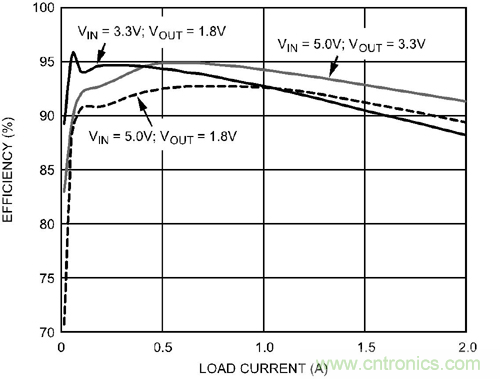

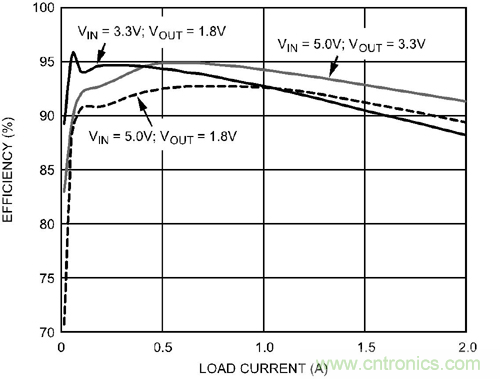

傳統(tǒng)上�����,開(kāi)關(guān)調(diào)節(jié)器不宜用于直接為ADC供電。然而��,開(kāi)關(guān)調(diào)節(jié)器技術(shù)已今非昔比����,當(dāng)與后置濾波��、精心的設(shè)計(jì)和布局布線做法相結(jié)合��,開(kāi)關(guān)調(diào)節(jié)器可以用作許多高速模數(shù)轉(zhuǎn)換器的高效率電源解決方案����。如圖2所示,開(kāi)關(guān)調(diào)節(jié)器的效率可達(dá)95%�����,相比于LDO��,系統(tǒng)功耗顯著降低�����。對(duì)于一個(gè)功耗為780mW的1.8V單電源ADC�����,如果使用開(kāi)關(guān)調(diào)節(jié)器電源,整體系統(tǒng)功耗可降低640mW或更多����。此外,開(kāi)關(guān)電源設(shè)計(jì)消除了線性級(jí)這一熱源����,PCB的總體熱量得以降低,因而對(duì)風(fēng)扇和散熱器等額外冷卻措施的需求會(huì)減少�����。

圖2:LDO為ADC供電��,包括濾波

不過(guò)�����,開(kāi)關(guān)調(diào)節(jié)器確實(shí)會(huì)產(chǎn)生噪聲��,必須通過(guò)精心的設(shè)計(jì)和布局布線予以控制����。開(kāi)關(guān)電源主要有兩類(lèi)噪聲:開(kāi)關(guān)紋波和高頻噪聲����。對(duì)于恒頻開(kāi)關(guān)調(diào)節(jié)器����,開(kāi)關(guān)紋波會(huì)在開(kāi)關(guān)頻率及其倍數(shù)頻率產(chǎn)生能量。高頻噪聲由轉(zhuǎn)換器中的電壓和電流快速跳變而產(chǎn)生�����。1-5ns的典型上升時(shí)間可以在70-350MHz區(qū)間內(nèi)產(chǎn)生能量�����。對(duì)這兩個(gè)噪聲源均必須進(jìn)行充分濾波�����,以免其干擾轉(zhuǎn)換器的工作��,降低轉(zhuǎn)換器的性能�����。這可能需要使用多級(jí)LC濾波器����,以降低紋波并衰減噪聲����。為保持直流調(diào)節(jié)能力,開(kāi)關(guān)電源控制環(huán)路可以在輸出濾波器的兩級(jí)附近閉合����。為保持穩(wěn)定性,環(huán)路穿越頻率必須較低�����。ADC給電源帶來(lái)的負(fù)載特性基本上是一個(gè)與時(shí)鐘頻率成正比的直流負(fù)載����。由于該負(fù)載是恒定的,開(kāi)關(guān)調(diào)節(jié)器的瞬態(tài)響應(yīng)相對(duì)不重要����,因此低環(huán)路穿越頻率在這種情況下是可以接受的。對(duì)調(diào)節(jié)器進(jìn)行外部補(bǔ)償可以更輕松實(shí)現(xiàn)這一目標(biāo)�����。

對(duì)輸出電源電壓上的噪聲進(jìn)行充分濾波至關(guān)重要,但設(shè)計(jì)人員也必須盡量減小從電源所含磁性元件(電感)到與ADC時(shí)鐘或信號(hào)路徑相關(guān)的巴倫或變壓器之間的磁場(chǎng)或電場(chǎng)耦合��。將電源電感放在PCB上的另一端并遠(yuǎn)離關(guān)鍵的ADC時(shí)鐘和輸入相關(guān)電路��,有助于減小這種耦合�����。

電源去耦

盡管高速ADC給電源帶來(lái)的總負(fù)載是穩(wěn)定的��,但需要電流以ADC采樣速率和此頻率的諧波快速跳變��。由于和走線的電感會(huì)限制電源能夠迅速提供的電流量����,因此ADC所需的高頻電流是由板電源去耦電容提供的��。為高速ADC供電時(shí)����,應(yīng)同時(shí)采用大的電源去耦電容和局部(ADC引腳處)去耦電容�����。大去耦電容存儲(chǔ)電荷以對(duì)電源層和局部去耦電容充電,局部去耦電容則提供ADC所需的高頻電流�����。有效的去耦還能將高頻電源瞬變限制在距離產(chǎn)生瞬變的IC非常近的區(qū)域��,從而使電路板上產(chǎn)生的電磁輻射()降至 �����。

一般而言�����,應(yīng)為每個(gè)ADC電源軌至少提供一個(gè)大去耦電容����。這些電容應(yīng)當(dāng)是10uF至22uF范圍內(nèi)的低ESR陶瓷或鉭電容。對(duì)于局部去耦����,一般建議為每個(gè)電源引腳提供一個(gè)去耦電容。局部去耦電容應(yīng)當(dāng)是0.01uF至0.1uF范圍內(nèi)的低ESR陶瓷電容��,并且應(yīng)盡可能靠近ADC電源引腳放置。這些電容應(yīng)具有通向電源層的過(guò)孔�����,并且過(guò)孔應(yīng)非?�?拷麬DC電源引腳�����。如果ADC是從PCB上緊密耦合的電源層獲得電源����,則局部去耦也可以通過(guò)層與層之間的電容效應(yīng)實(shí)現(xiàn)。如果這些層相對(duì)較大��,并且間隔小于5密爾(mil)����,則層間電容可提供非常有效的去耦作用�����。層間電容與局部旁路電容共同提供ADC所需的高頻電流����。

接地

ADC接地是電源方案的重要一環(huán)�����。當(dāng)前許多ADC都采用LFCSP封裝����,封裝底部有一個(gè)接地金屬塊�����。此金屬塊用于為器件散熱��;在許多情況下��,此接地金屬塊是器件 的接地連接�����。必須將此接地金屬塊焊接到上的接地焊盤(pán)����,此焊盤(pán)有多個(gè)過(guò)孔通向接地層。

ADC地上的噪聲也會(huì)影響其性能����。當(dāng)數(shù)字回路電流流經(jīng)ADC所在區(qū)域時(shí)����,通常會(huì)產(chǎn)生接地噪聲��。設(shè)計(jì)人員應(yīng)當(dāng)采取措施��,確保高噪聲地電流不會(huì)流經(jīng)ADC附近��。一般建議使用連續(xù)層��,但為了隔離高噪聲地電流�����,可能需要使用非連續(xù)層��。

結(jié)論

ADC的電源實(shí)現(xiàn)方案可能會(huì)對(duì)器件的性能產(chǎn)生重大影響�����。按照本文提出的指導(dǎo)原則進(jìn)行設(shè)計(jì)��,可以實(shí)現(xiàn)有效的ADC電源����。尋找特定ADC的電源參考資料時(shí),首先應(yīng)查看該ADC的評(píng)估板�����。ADI公司的所有ADC都有附帶電源的評(píng)估板��。研究評(píng)估板電源的結(jié)構(gòu)以及它所采用的去耦和布局�����,是開(kāi)展ADC電源設(shè)計(jì)的起點(diǎn)�����。

推薦閱讀: