【導(dǎo)讀】開(kāi)關(guān)電源因體積小、功率因數(shù)較大等優(yōu)點(diǎn),在通信、控制、計(jì)算機(jī)等領(lǐng)域應(yīng)用廣泛。但由于會(huì)產(chǎn)生電磁干擾,其進(jìn)一步的應(yīng)用受到一定程度上的限制。本文將分析開(kāi)關(guān)電源電磁干擾的各種產(chǎn)生機(jī)理,并在其基礎(chǔ)之上,提出開(kāi)關(guān)電源的電磁兼容設(shè)計(jì)方法。

開(kāi)關(guān)電源的電磁干擾分析

首先將工頻交流整流為直流,再逆變?yōu)楦哳l,最后再經(jīng)整流濾波電路輸出,得到穩(wěn)定的直流電壓。電路設(shè)計(jì)及布局不合理、機(jī)械振動(dòng)、接地不良等都會(huì)形成內(nèi)部電磁干擾。同時(shí),變壓器的漏感和輸出二極管的反向恢復(fù)電流造成的尖峰,也是潛在的強(qiáng)干擾源。

1.內(nèi)部干擾源

● 開(kāi)關(guān)電路

開(kāi)關(guān)電路主要由開(kāi)關(guān)管和高頻變壓器組成。開(kāi)關(guān)管及其散熱片與外殼和電源內(nèi)部的引線間存在分布電容,它產(chǎn)生的du/dt具有較大幅度的脈沖,頻帶較寬且諧波豐富。開(kāi)關(guān)管負(fù)載為高頻變壓器初級(jí)線圈,是感性負(fù)載。當(dāng)原來(lái)導(dǎo)通的開(kāi)關(guān)管關(guān)斷時(shí),高頻變壓器的漏感產(chǎn)生了反電勢(shì)E=-Ldi/dt,其值與集電極的電流變化率成正比,與漏感成正比,迭加在關(guān)斷電壓上,形成關(guān)斷電壓尖峰,從而形成傳導(dǎo)干擾?! ?/div>

● 整流電路的整流二極管

輸出整流二極管截止時(shí)有一個(gè)反向電流,其恢復(fù)到零點(diǎn)的時(shí)間與結(jié)電容等因素有關(guān)。它會(huì)在變壓器漏感和其他分布參數(shù)的影響下產(chǎn)生很大的電流變化di/dt,產(chǎn)生較強(qiáng)的高頻干擾,頻率可達(dá)幾十兆赫茲。

● 雜散參數(shù)

由于工作在較高頻率,開(kāi)關(guān)電源中的低頻元器件特性會(huì)發(fā)生變化,由此產(chǎn)生噪聲。在高頻時(shí),雜散參數(shù)對(duì)耦合通道的特性影響很大,而分布電容成為電磁干擾的通道。

2.外部干擾源

外部干擾源可以分為電源干擾和雷電干擾,而電源干擾以“共模”和“差模”方式存在。同時(shí),由于交流電網(wǎng)直接連到整流橋和濾波電路上,在半個(gè)周期內(nèi),只有輸入電壓的峰值時(shí)間才有輸入電流,導(dǎo)致電源的輸入功率因數(shù)很低(大約為0.6)。而且,該電流含有大量電流諧波分量,會(huì)對(duì)電網(wǎng)產(chǎn)生諧波“污染”。

開(kāi)關(guān)電源的EMC設(shè)計(jì)

產(chǎn)生電磁干擾有3個(gè)必要條件:干擾源、傳輸介質(zhì)、敏感設(shè)備,EMC設(shè)計(jì)的目的就是破壞這3個(gè)條件中的一個(gè)。針對(duì)于此,主要采取的方法有:電路措施、EMI濾波、屏蔽、印制電路板抗干擾設(shè)計(jì)等。

1.降低開(kāi)關(guān)損耗和開(kāi)關(guān)噪聲的軟開(kāi)關(guān)技術(shù)

軟開(kāi)關(guān)是在硬開(kāi)關(guān)基礎(chǔ)上發(fā)展起來(lái)的一種基于諧振技術(shù)或利用控制技術(shù)實(shí)現(xiàn)的在零電壓/電流狀態(tài)下的先進(jìn)開(kāi)關(guān)技術(shù)。

軟開(kāi)關(guān)的實(shí)現(xiàn)方法是:在原電路中增加小電感、電容等諧振元件,在開(kāi)關(guān)過(guò)程前后引入諧振,消除電壓、電流的重疊。圖2給出了一種使用軟開(kāi)關(guān)技術(shù)的基本開(kāi)關(guān)單元。

2.減小干擾源干擾能量的緩沖電路

在開(kāi)關(guān)控制電源的輸入部分加入緩沖電路,其由線性阻抗穩(wěn)定網(wǎng)絡(luò)組成,用于消除電力線干擾、電快速瞬變、電涌、電壓高低變化和電力線諧波等潛在的干擾。緩沖電路器件參數(shù)為R1=500Ω,C=6nF,L=36mH,R=150Ω。

3.切斷干擾噪聲傳播路徑的EMI濾波

在開(kāi)關(guān)電源輸入和輸出電路中加裝EMI濾波器,是抑制傳導(dǎo)發(fā)射的一個(gè)很有效方法。其參數(shù)主要有:放電電阻、插入損耗、Cx電容、Cy電容和電感值。其中,插入損耗是濾波器性能的一個(gè)關(guān)鍵參數(shù)。在考慮機(jī)械性能、環(huán)境、成本等前提下,應(yīng)該盡量使插入損耗大一些。用共模、差模干擾的測(cè)量結(jié)果與標(biāo)準(zhǔn)限值,加上適當(dāng)?shù)脑A靠傻玫綖V波器的插入損耗IL。

ILCM(dB)=Vcm(dB)-Vlimt(dB)-3(dB)+M(dB) (1)

ILDM(dB)=VDM(dB)-Vlimt(dB)-3(dB)+M(dB) (2)

式中,3dB表示在分離共模、差模傳導(dǎo)干擾的測(cè)試過(guò)程中測(cè)試結(jié)果比實(shí)際值大3dB;

M(dB)表示設(shè)計(jì)裕量,一般取6dB;Vlimit(dB)為相關(guān)標(biāo)準(zhǔn)如CISPR,FCC等規(guī)定的傳導(dǎo)干擾限值。

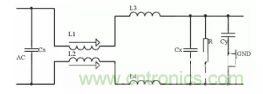

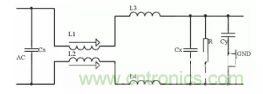

圖4是220V/50Hz交流輸入的開(kāi)關(guān)電源交流側(cè)EMI濾波器的電路。Cy=3300pF,L1、L2=0.7mH,它們構(gòu)成共模濾波電路,抑制0.5~30MHz的共模干擾信號(hào)。Cx=0.1μF,L3、L4=200~500μH,采用金屬粉壓磁芯,與L1/L2、Cx構(gòu)成L-N端口間低通濾波器,用于抑制電源線上存在的0.15~ 0.5MHz差模干擾信號(hào)。R用于消除可能在濾波器中出現(xiàn)的靜電積累。

圖4:開(kāi)關(guān)電源交流側(cè)EMI濾波器電路

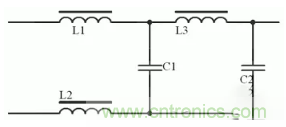

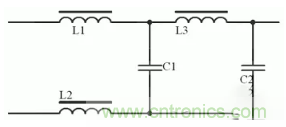

圖5是開(kāi)關(guān)電源的直流輸出側(cè)濾波電路,它由共模扼流圈L1、L2,扼流圈L3和電容C1、C2組成。為了防止磁芯在較大的磁場(chǎng)強(qiáng)度下飽和而使扼流圈失去作用,磁芯必須采用高頻特性好且飽和磁場(chǎng)強(qiáng)度大的恒μ磁芯。

圖5:支流側(cè)濾波電路

4.用屏蔽來(lái)抑制輻射及感應(yīng)干擾

開(kāi)關(guān)電源干擾頻譜集中在30MHz以下的頻段,直徑r<λ/2π,主要是近場(chǎng)性質(zhì)的電磁場(chǎng),且屬低阻抗場(chǎng)??捎脤?dǎo)電良好的材料對(duì)電場(chǎng)屏蔽,而用導(dǎo)磁率高的材料對(duì)磁場(chǎng)屏蔽。此外,還要對(duì)變壓器、電感器、功率器件等采取有效的屏蔽措施。屏蔽外殼上的通風(fēng)孔最好為圓形,在滿足通風(fēng)的條件下,孔的數(shù)量可以多,每個(gè)孔的尺寸要盡可能小。接縫處要焊接,以保證電磁的連續(xù)性。屏蔽外殼的引入、引出線處要采取濾波措施。對(duì)于電場(chǎng)屏蔽,屏蔽外殼一定要接地。對(duì)于磁場(chǎng)屏蔽,屏蔽外殼不需接地。

5.合理的PCB布局及布線

敏感線路主要是指控制電路和直接與干擾測(cè)量設(shè)備相連的線路。要降低干擾水平,最簡(jiǎn)單的方法就是增大干擾源與敏感線路的間距。但由于受電源尺寸的限制,單純的增大間距并非解決問(wèn)題的最佳途徑,更為合理的方法是根據(jù)干擾電場(chǎng)的分布情況將敏感線路放在干擾較弱的地方。PCB抗干擾布局設(shè)計(jì)流程如圖6所示。

圖6:PCB抗干擾布局設(shè)計(jì)流程

以上內(nèi)容均來(lái)源于網(wǎng)絡(luò)