【導讀】當一塊原型電源板首次加電時,最好的情況是它不僅能工作,而且還安靜、發(fā)熱低。然而,這種情況并不多見。一個良好的布局設計可優(yōu)化效率,減緩熱應力,并盡量減小走線與元件之間的噪聲與作用。這一切都源于設計人員對電源中電流傳導路徑以及信號流的理解。

開關電源的一個常見問題是“不穩(wěn)定”的開關波形。有些時候,波形抖動處于聲波段,磁性元件會產生出音頻噪聲。如果問題出在印刷電路板的布局上,要找出原因可能會很困難。因此,開關電源設計初期的正確PCB布局就非常關鍵。

電源設計者要很好地理解技術細節(jié),以及最終產品的功能需求。因此,從電路板設計項目一開始,電源設計者應就關鍵性電源布局,與PCB布局設計人員展開密切合作。

一個好的布局設計可優(yōu)化電源效率,減緩熱應力;更重要的是,它最大限度地減小了噪聲,以及走線與元件之間的相互作用。為實現(xiàn)這些目標,設計者必須了解開關電源內部的電流傳導路徑以及信號流。要實現(xiàn)非隔離開關電源的正確布局設計,務必牢記以下這些設計要素。

布局規(guī)劃

對一塊大電路板上的嵌入dc/dc電源,要獲得最佳的電壓調節(jié)、負載瞬態(tài)響應和系統(tǒng)效率,就要使電源輸出靠近負載器件,盡量減少PCB走線上的互連阻抗和傳導壓降。確保有良好的空氣流,限制熱應力;如果能采用強制氣冷措施,則要將電源靠近風扇位置。

另外,大型無源元件(如電感和電解電容)均不得阻擋氣流通過低矮的表面封裝半導體元件,如功率MOSFET或PWM控制器。為防止開關噪聲干擾到系統(tǒng)中的模擬信號,應盡可能避免在電源下方布放敏感信號線;否則,就需要在電源層和小信號層之間放置一個內部接地層,用做屏蔽。

關鍵是要在系統(tǒng)早期設計和規(guī)劃階段,就籌劃好電源的位置,以及對電路板空間的需求。有時設計者會無視這種忠告,而把關注點放在大型系統(tǒng)板上那些更“重要”或“讓人興奮”的電路。電源管理被看作事后工作,隨便把電源放在電路板上的多余空間上,這種做法對高效率而可靠的電源設計十分不利。

對于多層板,很好的方法是在大電流的功率元件層與敏感的小信號走線層之間布放直流地或直流輸入/輸出電壓層。地層或直流電壓層提供了屏蔽小信號走線的交流地,使其免受高噪聲功率走線和功率元件的干擾。

作為一般規(guī)則,多層PCB板的接地層或直流電壓層均不應被分隔開。如果這種分隔不可避免,就要盡量減少這些層上走線的數(shù)量和長度,并且走線的布放要與大電流保持相同的方向,使影響最小化。

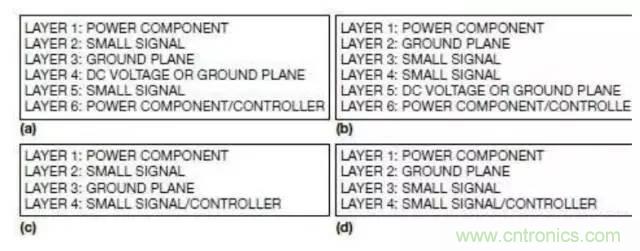

圖1a和1c分別是六層和四層開關電源PCB的不良層結構。這些結構將小信號層夾在大電流功率層和地層之間,因此增加了大電流/電壓功率層與模擬小信號層之間耦合的電容噪聲。

圖中的1b和1d則分別是六層和四層PCB設計的良好結構,有助于最大限度減少層間耦合噪聲,地層用于屏蔽小信號層。要點是:一定要挨著外側功率級層放一個接地層,外部大電流的功率層要使用厚銅箔,盡量減少PCB傳導損耗和熱阻。

功率級的布局

開關電源電路可以分為功率級電路和小信號控制電路兩部分。功率級電路包含用于傳輸大電流的元件,一般情況下,要首先布放這些元件,然后在布局的一些特定點上布放小信號控制電路。

大電流走線應短而寬,盡量減少PCB的電感、電阻和壓降。對于那些有高di/dt脈沖電流的走線,這方面尤其重要。

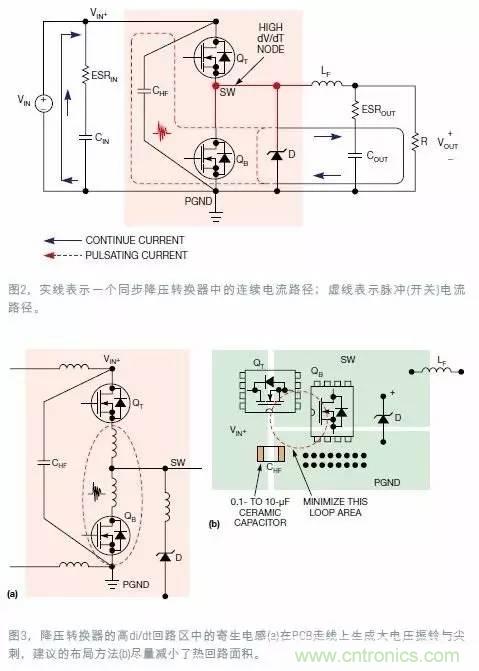

圖2給出了一個同步降壓轉換器中的連續(xù)電流路徑和脈沖電流路徑,實線表示連續(xù)電流路徑,虛線代表脈沖(開關)電流路徑。脈沖電流路徑包括連接到下列元件上的走線:輸入去耦陶瓷電容CHF,上部控制FET QT以及下部同步FET QB,還有選接的并聯(lián)肖特基二極管。

圖3a給出了高di/dt電流路徑中的PCB寄生電感。由于存在寄生電感,因此脈沖電流路徑不僅會輻射磁場,而且會在PCB走線和MOSFET上產生大的電壓振鈴和尖刺。為盡量減小PCB電感,脈沖電流回路(所謂熱回路)布放時要有最小的圓周,其走線要短而寬。

高頻去耦電容CHF應為0.1μF~10μF,X5R或X7R電介質的陶瓷電容,它有極低的ESL(有效串聯(lián)電感)和ESR(等效串聯(lián)電阻)。較大的電容電介質(如Y5V)可能使電容值在不同電壓和溫度下有大的下降,因此不是CHF的最佳材料。

圖3b為降壓轉換器中的關鍵脈沖電流回路提供了一個布局例子。為了限制電阻壓降和過孔數(shù)量,功率元件都布放在電路板的同一面,功率走線也都布在同一層上。當需要將某根電源線走到其它層時,要選擇在連續(xù)電流路徑中的一根走線。當用過孔連接大電流回路中的PCB層時,要使用多個過孔,盡量減小阻抗。

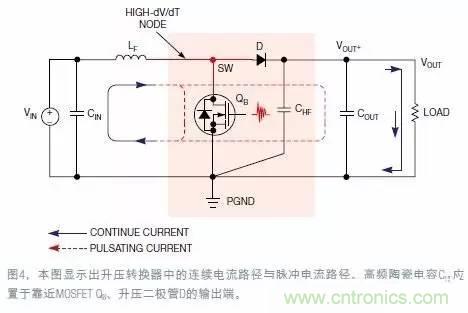

圖4顯示的是升壓轉換器中的連續(xù)電流回路與脈沖電流回路。此時,應在靠近MOSFET QB與升壓二極管D的輸出端放置高頻陶瓷電容CHF。

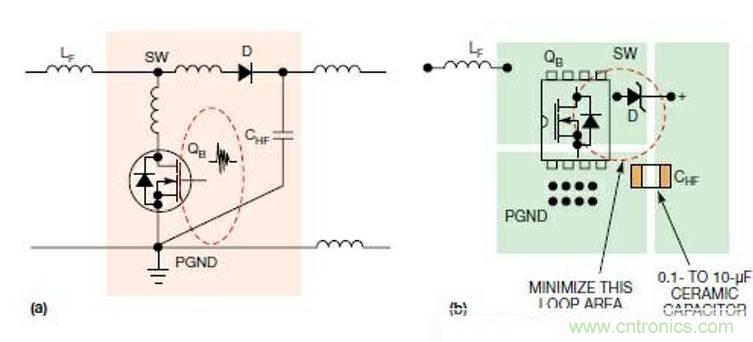

圖5 顯示的是升壓轉換器中的熱回路與寄生PCB電感(a);為減少熱回路面積而建議采用的布局(b)

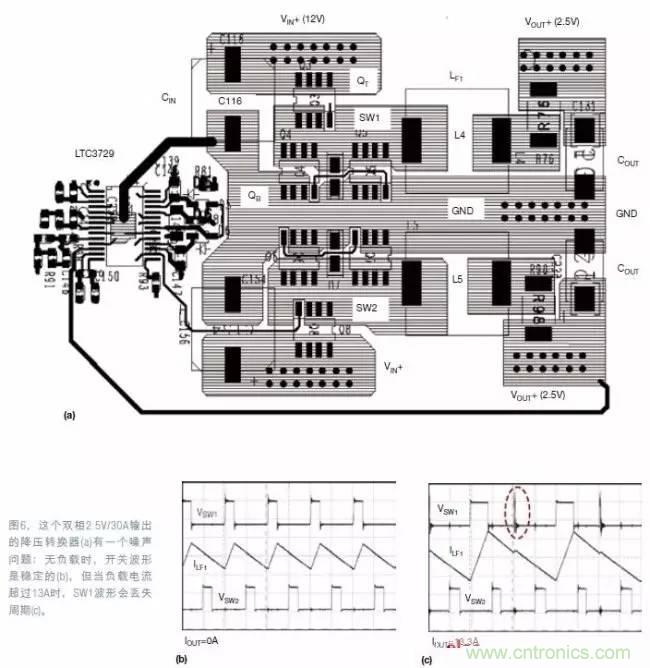

圖5是升壓轉換器中脈沖電流回路的一個布局例子。此時關鍵在于盡量減小由開關管QB、整流二極管D和高頻輸出電容CHF形成的回路。圖6提供了一個同步降壓電路的例子,它強調了去耦電容的重要性。圖6a是一個雙相12VIN、 2.5VOUT/30A(最大值)的同步降壓電源,使用了LTC3729雙相單VOUT控制器IC,在無負載時,開關結點SW1和SW2的波形以及輸出電感電流都是穩(wěn)定的(圖6b)。但如果負載電流超過13A,SW1結點的波形就開始丟失周期。負載電流更高時,問題會更惡化(圖6c)。

在各個通道的輸入端增加兩只1μF的高頻陶瓷電容,就可以解決這個問題,電容隔離開了每個通道的熱回路面積,并使之最小化。即使在高達30A的最大負載電流下,開關波形仍很穩(wěn)定。

高DV/DT開關區(qū)

圖2和圖4中,在VIN(或VOUT)與地之間的SW電壓擺幅有高的dv/dt速率。這個結點上有豐富的高頻噪聲分量,是一個強大的EMI噪聲源。為了盡量減小開關結點與其它噪聲敏感走線之間的耦合電容,你可能會讓SW銅箔面積盡可能小。但是,為了傳導大的電感電流,并且為功率MOSFET管提供散熱區(qū),SW結點的PCB區(qū)域又不能夠太小。一般建議在開關結點下布放一個接地銅箔區(qū),提供額外的屏蔽。

如果設計中沒有用于表面安裝功率MOSFET與電感的散熱器,則銅箔區(qū)必須有足夠的散熱面積。對于直流電壓結點(如輸入/輸出電壓與電源地),合理的方法是讓銅箔區(qū)盡可能大。

多過孔有助于進一步降低熱應力。要確定高dv/dt開關結點的合適銅箔區(qū)面積,就要在盡量減小dv/dt相關噪聲與提供良好的MOSFET散熱能力兩者間做一個設計平衡。

功率焊盤形式

注意功率元件的焊盤形式,如低ESR電容、MOSFET、二極管和電感。

對于去耦電容,正負極過孔應盡量互相靠近,以減少PCB的ESL。這對低ESL電容尤其有效。小容值低ESR的電容通常較貴,不正確的焊盤形式及不良走線都會降低它們的性能,從而增加整體成本。通常情況下,合理的焊盤形式能降低PCB噪聲,減小熱阻,并最大限度降低走線阻抗以及大電流元件的壓降。

大電流功率元件布局時有一個常見的誤區(qū),那就是不正確地采用了熱風焊盤(thermal relief)。非必要情況下使用熱風焊盤,會增加功率元件之間的互連阻抗,從而造成較大的功率損耗,降低小ESR電容的去耦效果。如果在布局時用過孔來傳導大電流,要確保它們有充足的數(shù)量,以減少阻抗。此外,不要對這些過孔使用熱風焊盤。

控制電路布局

使控制電路遠離高噪聲的開關銅箔區(qū)。對降壓轉換器,好的辦法是將控制電路置于靠近VOUT+端,而對升壓轉換器,控制電路則要靠近VIN+端,讓功率走線承載連續(xù)電流。

如果空間允許,控制IC與功率MOSFET及電感(它們都是高噪聲高熱量元件)之間要有小的距離(0.5英寸~1英寸)。如果空間緊張,被迫將控制器置于靠近功率MOSFET與電感的位置,則要特別注意用地層或接地走線,將控制電路與功率元件隔離開來。

控制電路應有一個不同于功率級地的獨立信號(模擬)地。如果控制器IC上有獨立的SGND(信號地)和PGND(功率地)引腳,則應分別布線。對于集成了MOSFET驅動器的控制IC,小信號部分的IC引腳應使用SGND。

信號地與功率地之間只需要一個連接點。合理方法是使信號地返回到功率地層的一個干凈點。只在控制器 IC下連接兩種接地走線,就可以實現(xiàn)兩種地。

控制IC的去耦電容應靠近各自的引腳。為盡量減少連接阻抗,好的方法是將去耦電容直接接到引腳上,而不通過過孔。

回路面積與串擾

兩個或多個鄰近導體可以產生容性耦合。一個導體上的高dv/dt會通過寄生電容,在另一個導體上耦合出電流。為減少功率級對控制電路的耦合噪聲,高噪聲的開關走線要遠離敏感的小信號走線。如果可能的話,要將高噪聲走線與敏感走線布放在不同的層,并用內部地層作為噪聲屏蔽。

空間允許的話,控制IC要距離功率MOSFET和電感有一個小的距離(0.5英寸~1英寸),后者既有大噪聲又發(fā)熱。

LTC3855控制器上的FET驅動器TG、BG、SW和BOOST引腳都有高的dv/dt開關電壓。連接到最敏感小信號結點的LTC3855引腳是:Sense+/Sense-、FB、ITH和SGND,如果布局時將敏感的信號走線靠近了高dv /dt結點,則必須在信號走線與高dv/dt走線之間插入接地線或接地層,以屏蔽噪聲。

在布放柵極驅動信號時,采用短而寬的走線有助于盡量減小柵極驅動路徑中的阻抗。

如果在BG走線下布放了一個PGND層,低FET的交流地返回電流將自動耦合到一個靠近BG走線的路徑中。交流電流會流向它所發(fā)現(xiàn)的最小回路/阻抗。此時,低柵極驅動器不需要一個獨立的PGND返回走線。最好的辦法是盡量減少柵極驅動走線通過的層數(shù)量,這樣可防止柵極噪聲傳播到其它層。

在所有小信號走線中,電流檢測走線對噪聲最為敏感。電流檢測信號的波幅通常小于100mV,這與噪聲的波幅相當。以LTC3855為例,Sense+/Sense-走線應以最小間距并行布放(Kelvin檢測),以盡量減少拾取di/dt相關噪聲的機會。

另外,電流檢測走線的濾波電阻與電容都應盡可能靠近IC引腳。當有噪聲注入長的檢測線時,這種結構的濾波效果最好。如果采用帶R/C網絡的電感DCR電流檢測方式,則DCR檢測電阻R應靠近電感,而DCR檢測電容C則應靠近IC。

如果在走線到Sense-的返回路徑上使用了一個過孔,則過孔不應接觸到其它的內部VOUT+層。否則,過孔可能會傳導大的VOUT+電流,所產生的壓降可能破壞電流檢測信號。要避免在高噪聲開關結點(TG、BG、SW和BOOST走線)附近布放電流檢測走線。如可能,在電流檢測走線所在層與功率級走線層之間放置地層。

如果控制器IC有差分電壓遠程檢測引腳,則要為正、負遠程檢測線采用獨立的走線,同時也采用Kelvin檢測連接。

走線寬度的選擇

對具體的控制器引腳,電流水平和噪聲敏感度都是唯一的,因此,必須為不同信號選擇特定的走線寬度。通常情況下,小信號網絡可以窄些,采用10mil~15mil寬度的走線;大電流網絡(柵極驅動、VCC以及PGND)則應采用短而寬的走線。這些網絡的走線建議至少為20mil寬。

本文轉載自電源研發(fā)精英圈。

推薦閱讀: