【導(dǎo)讀】視頻系統(tǒng),目前已經(jīng)深入消費應(yīng)用的各個方面,在汽車、機(jī)器人和工業(yè)領(lǐng)域日益普遍。其在非消費應(yīng)用中的增長主要源于HDMI標(biāo)準(zhǔn)以及更快、更高效的DSP和FPGA的出現(xiàn)。

本文將概要討論利用模擬或HDMI攝像機(jī)實現(xiàn)立體視覺(3D視頻)的各種要求。文章將描述一個基于FPGA的系統(tǒng),它將兩個視頻流結(jié)合成一個3D視頻流,通過HDMI 1.4發(fā)射器進(jìn)行傳輸,同時還要介紹一個基于DSP的系統(tǒng),與通常需從兩臺攝像機(jī)接收數(shù)據(jù)相比,該系統(tǒng)可以節(jié)省DMA帶寬。另外,本文還將描述一種方法,該方法可以實現(xiàn)一種并排格式,可供3D攝像機(jī)或要求3D視頻的系統(tǒng)使用。

概述

立體視覺要求使用兩臺攝像機(jī),二者相距大約5.5厘米,這是人類雙眼之間的典型間距,如圖1所示。

圖1 支架上的兩臺攝像機(jī)(已針對立體視覺對齊)

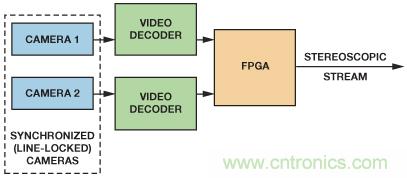

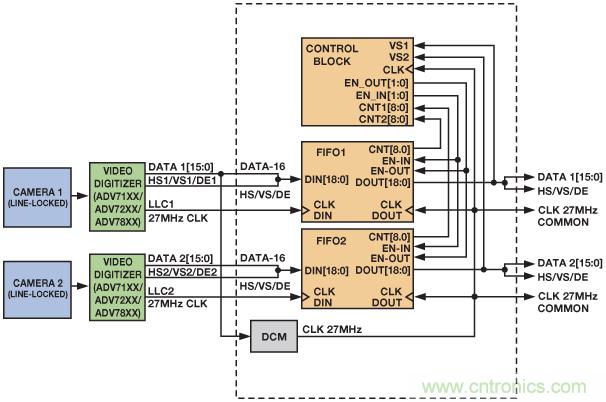

圖2所示高級功能框圖使用了采用相同視頻標(biāo)準(zhǔn)的兩臺同步攝像機(jī)、兩個視頻解碼器和一個FPGA。為了確保完全一致的幀速率,攝像機(jī)必須行鎖定到共同的參考時序。如果沒有同步,不使用外部存儲器,就不可能將輸出組合起來并存儲為完整的視頻幀。

圖2 高級功能框圖

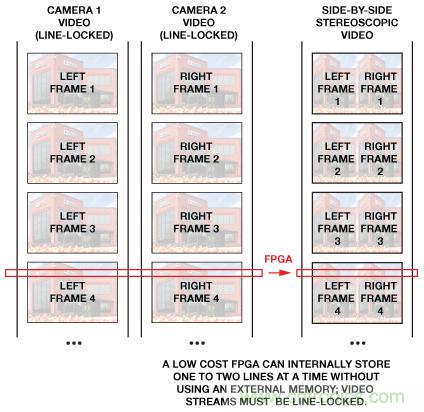

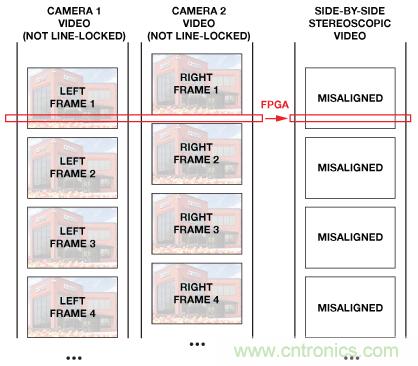

圖3顯示兩個行鎖定視頻流被合并成一個立體圖像。圖4顯示,如果不將整個視頻幀保存在外部存儲器中,則異步視頻流無法合并。

圖3 合并兩個同步視頻流

圖4 如果不使用外部存儲器,則無法合并異步視頻流

然后,兩臺同步攝像機(jī)的輸出由視頻解碼器(如ADV7181D, ADV7182或ADV7186 用于模擬攝像機(jī))進(jìn)行數(shù)字化處;也可由 HDMI receivers(如ADV7610 或 ADV7611用于數(shù)字?jǐn)z像機(jī))進(jìn)行數(shù)字化處理。

視頻解碼器和HDMI接收器都采用內(nèi)部鎖相環(huán)(PLL)在其輸出總線上產(chǎn)生時鐘和像素數(shù)據(jù)。這意味著,在數(shù)字化模擬視頻,或者接收HDMI流時,將為兩臺攝像機(jī)產(chǎn)生兩個獨立的時鐘域。另外,兩個視頻流可能存在對齊誤差。這些時序差異和對齊誤差必須在后端器件(如FPGA)中進(jìn)行補(bǔ)償,先將數(shù)據(jù)帶至共同的時鐘域,然后再將兩個視頻圖像結(jié)合成單個立體視頻幀。然后,通過一個支持3D的HDMI 1.4HDMI 接收器(如ADV7511 或 ADV7513—也可以將其提供給DSP(如 ADSP-BF609 Blackfin®處理器)—以便進(jìn)一步處理。

時鐘架構(gòu)

視頻解碼器有兩種完全不同的時鐘源,具體取決于其是否鎖定。當(dāng)視頻PLL被鎖定至輸入同步信號時——水平同步(視頻解碼器)或TMDS時鐘(HDMI)——結(jié)果會產(chǎn)生一個鎖定至輸入視頻源的時鐘。當(dāng)視頻失鎖時,或者當(dāng)PLL處于強(qiáng)制自由運行模式時,視頻PLL不會鎖定至輸入同步信號,結(jié)果會產(chǎn)生一個鎖定至晶振時鐘的時鐘輸出。另外,時鐘可能不會在復(fù)位后輸出,因為LLC時鐘驅(qū)動器在復(fù)位后設(shè)置為高阻抗模式。

因此,如果系統(tǒng)有兩個或多個始于視頻解碼器或HDMI接收器的視頻路徑,即使將同一晶振時鐘提供給兩個視頻解碼器或HDMI接收器,仍會有兩個不同頻率、不同相位的不同時鐘域,因為每個器件都會基于自己的PLL產(chǎn)生自己的時鐘。

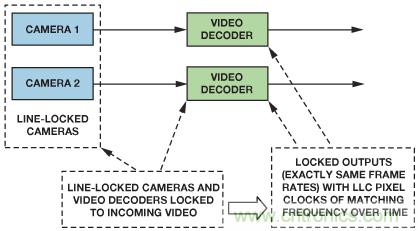

帶鎖定視頻解碼器的同步系統(tǒng)

典型的立體視頻使用兩個視頻源,其中,每個視頻解碼器都會鎖定至輸入視頻信號,并會基于輸入水平同步或TMDS時鐘產(chǎn)生自己的時鐘。當(dāng)兩臺攝像機(jī)同步——或行鎖定至同一參考時序時——分幀線將始終對齊。由于兩個獨立的視頻解碼器會收到相同的水平同步信號,因此,像素時鐘將擁有相同的像素時鐘頻率。這樣,就可以將兩條數(shù)據(jù)路徑帶入同一個時鐘域,如圖5所示。

圖5 同步至同一參考源的兩臺攝像機(jī)。

兩個視頻解碼 器都會收到同一同步信號,因此,它們也會鎖定

異步視頻系統(tǒng)

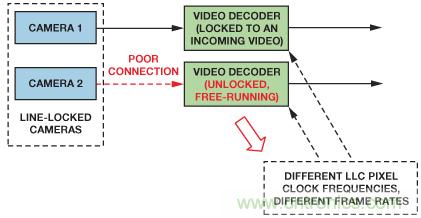

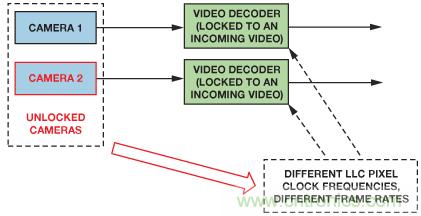

不幸的是,其中一個視頻解碼器可能因視頻源信號質(zhì)量欠佳而失鎖,如圖6所示;或者,攝像機(jī)因視頻鏈路斷開而失去同步性,如圖7所示。這會在兩條數(shù)據(jù)路徑中導(dǎo)致不同的頻率,結(jié)果又會導(dǎo)致進(jìn)入后端中的數(shù)據(jù)量不對稱。

圖6 帶未鎖定視頻解碼器的行鎖定攝像機(jī)

圖7 帶鎖定視頻解碼器的未鎖定攝像機(jī)

視頻失鎖可以通過使用一個中斷(SD視頻解碼器為SD_UNLOCK,分量視頻解碼器為CP_UNLOCK,或HDMI接收器中的TMDSPLL_LCK寄存器)來檢測,該中斷會在一定延遲后介入。視頻解碼器集成了不穩(wěn)定水平同步平滑機(jī)制,因此,視頻失鎖的檢測可能需要兩三行。該延遲可通過控制FPGA中的失鎖來減少。

時鐘三態(tài)模式

在設(shè)計FPGA時鐘資源時,必須知道,默認(rèn)情況下,許多視頻解碼器和HDMI產(chǎn)品在復(fù)位后將時鐘和數(shù)據(jù)線路置為三態(tài)模式。因此,LLC像素時鐘不適用于同步復(fù)位。

兩條視頻流中的數(shù)據(jù)對齊誤差

為了簡化系統(tǒng)并減少合并兩幅圖像所需存儲器,到達(dá)FPGA的數(shù)據(jù)應(yīng)進(jìn)行同步,以使來自第一臺攝像機(jī)的第M 行第N個 像素與來自第二臺攝像機(jī)的第M 行第N個 像素同時收到。

在FPGA輸入端,這可能很難實現(xiàn),因為兩條視頻路徑可能具有不同的延遲:行鎖定攝像機(jī)可能輸出存在對齊誤差的行,不同的連接長度可能加大對齊誤差,而視頻解碼器則可能帶來可變啟動延遲。受這些延遲影響,采用行鎖定攝像機(jī)的系統(tǒng)會有一些存在對齊誤差的像素。

行鎖定攝像機(jī)對齊誤差

即使是行鎖定攝像機(jī)也可能輸出存在對齊誤差的視頻行。圖8顯示來自兩臺攝像機(jī)的CVBS輸出端的垂直同步信號。一臺攝像機(jī)(同步主機(jī))為第二臺攝像機(jī)(同步從機(jī))提供行鎖定信號。380 ns的對齊誤差是清楚可見的。圖9展示的是這些攝像機(jī)輸出端的視頻解碼器傳輸?shù)臄?shù)據(jù)??梢钥吹?1個像素的位移。

圖8 行鎖定視頻攝像機(jī)之間的380 ns視頻對齊誤差

圖9 數(shù)字域中未補(bǔ)償?shù)?1個像素的視頻對齊誤差

不同的連接長度

所有電氣連接都會帶來傳播延遲,因此,要確保兩條視頻路徑具有相同的軌道和電纜長度。

視頻解碼器/HDMI接收器延遲

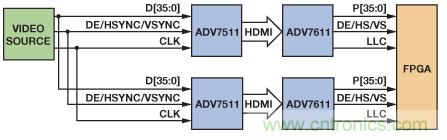

所有視頻解碼器都會帶來可能因啟用的功能而異的延遲。另外,有些視頻器件含有可能增加隨機(jī)啟動延遲的因素——如深色FIFO。采用視頻解碼器的典型立體系統(tǒng)的隨機(jī)啟動延遲大約為5個像素時鐘。含有HDMI發(fā)射器和接收器的系統(tǒng)(如圖10所示)的隨機(jī)啟動延遲可能為40個像素時鐘左右。

圖10 流水線延遲測量設(shè)置

對齊誤差補(bǔ)償

圖11所示系統(tǒng)中,一個視頻解碼器對來自各攝像機(jī)的模擬信號進(jìn)行數(shù)字化處理。各視頻路徑的數(shù)據(jù)和時鐘是獨立的。兩條視頻路徑都連接至FIFO,后者對輸入數(shù)據(jù)進(jìn)行緩沖,以補(bǔ)償數(shù)據(jù)對齊誤差。在輸出數(shù)據(jù)時,F(xiàn)IFO使用來自其中一個解碼器的共用時鐘。在鎖定系統(tǒng)中,兩條數(shù)據(jù)路徑應(yīng)具有完全相同的時鐘頻率,以確保在攝像機(jī)行鎖定且視頻解碼器鎖定的情況下,不會出現(xiàn)FIFO溢出或下溢現(xiàn)象。

通過啟用或禁用FIFO輸出,控制模塊可以維持FIFO電平以盡量減少像素對齊誤差。如果采取了正確的補(bǔ)償措施,則FPGA模塊的輸出應(yīng)為與第一個像素對齊的兩條數(shù)據(jù)路徑。然后該數(shù)據(jù)提供給FPGA后端,以生成3D格式。

圖11 使用數(shù)字FIFO來重新對齊視頻圖像

對齊誤差測量

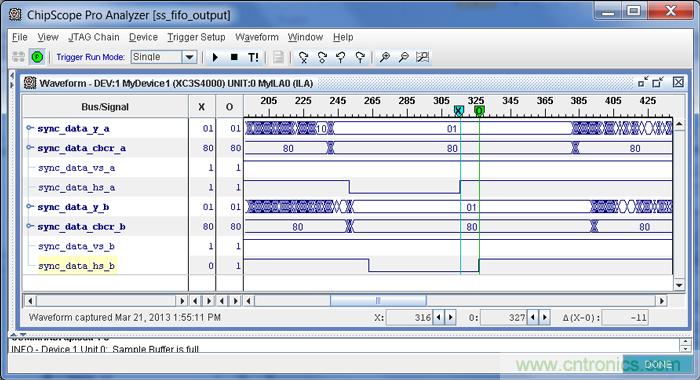

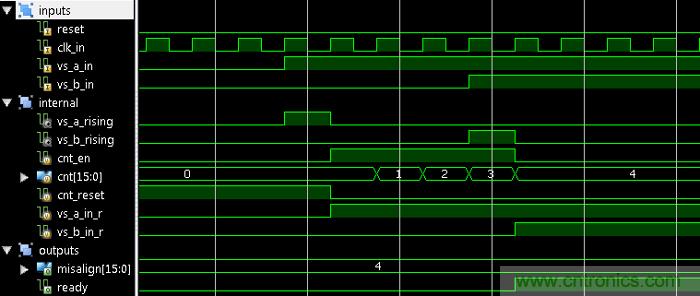

兩個數(shù)字化數(shù)據(jù)流之間的對齊誤差可以在視頻FIFO輸出端進(jìn)行測量,其方法是使用一個單一時鐘計數(shù)器,該計數(shù)器在輸入信號之一的垂直同步(VS)脈沖上復(fù)位。圖12所示兩個視頻流(vs_a_in和vs_b_in)的對齊誤差為4個像素。計數(shù)器使用列表1中所示方法測量對齊誤差。計數(shù)從VS1的上升沿開始,并在VS2的上升沿終止。

如果一個幀的總像素長度是已知的,則可以通過從幀長中減去計數(shù)值,從而算出負(fù)偏斜(VS2位于VS1之前)。該負(fù)值應(yīng)在偏斜超過像素幀長的一半時計算。結(jié)果應(yīng)用來重新對齊FIFO中存儲的數(shù)據(jù)。

圖12 對齊誤差測量

列表1 簡單對齊誤差測量(Verilog®).

module misalign_measurement(

input wire reset,

input wire clk_in,

input wire vs_a_in,

input wire vs_b_in,

output reg [15:0] misalign,

output reg ready);

reg [15:0] cnt;

reg cnt_en, cnt_reset;

reg vs_a_in_r, vs_b_in_r;

assign vs_a_rising = vs_a_in > vs_a_in_r;

assign vs_b_rising = vs_b_in > vs_b_in_r;

always @(posedge clk_in)

begin

vs_a_in_r <= vs_a_in;

vs_b_in_r <= vs_b_in;

end

always @(posedge clk_in)

if (reset)

begin

{ ready, cnt_en } <= 2''''b00;

misalign <= 0;

end else begin

if ((vs_a_in == 1''''b0) && (vs_b_in == 1''''b0))

{ ready, cnt_reset } <= 2''''b01;

else

cnt_reset <= 1''''b0;

/* beginning */

if (vs_a_rising && vs_b_rising)

begin

misalign <= 0;

{ ready, cnt_en } <= 2''''b10;

end

else if ((vs_a_rising > vs_b_in) || (vs_b_rising > vs_a_in))

{ ready, cnt_en } <= 2''''b01;

/* ending */

if ((cnt_en == 1''''b1) && (vs_a_rising || vs_b_rising))

begin

{ ready, cnt_en } <= 2''''b10;

misalign <= vs_a_rising ? (-(cnt + 1)) : (cnt + 1);

end

end

always @(posedge clk_in) /* counter */

if ((cnt_reset) || (reset))

cnt <= 0;

else if (cnt_en)

cnt <= cnt + 1;

endmodule

從兩個對齊視頻流生成3D視頻

一旦像素、行和幀數(shù)據(jù)都真正同步,F(xiàn)PGA可以將視頻數(shù)據(jù)轉(zhuǎn)換成3D視頻流,如圖13所示。

圖13 用于實現(xiàn)3D格式的簡化架構(gòu)

輸入數(shù)據(jù)由共用時鐘讀入存儲器。同步時序分析儀檢查輸入的同步信號,并抽取視頻時序,包括水平前后沿長度、垂直前后沿、水平和垂直同步長度、水平有效行長、垂直有效行數(shù)和同步信號極化。將該信息與當(dāng)前水平和垂直像素位置一起傳給同步時序再發(fā)生器,這樣可以生成經(jīng)修改的時序,以便支持所需3D視頻結(jié)構(gòu)。新生成的時序應(yīng)延遲,以確保FIFO含有所需數(shù)據(jù)量。

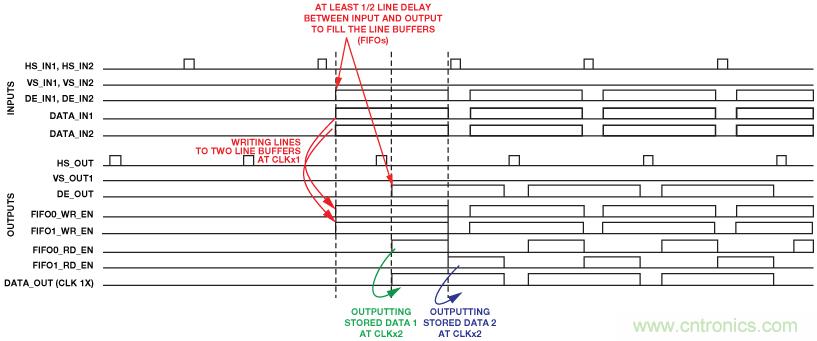

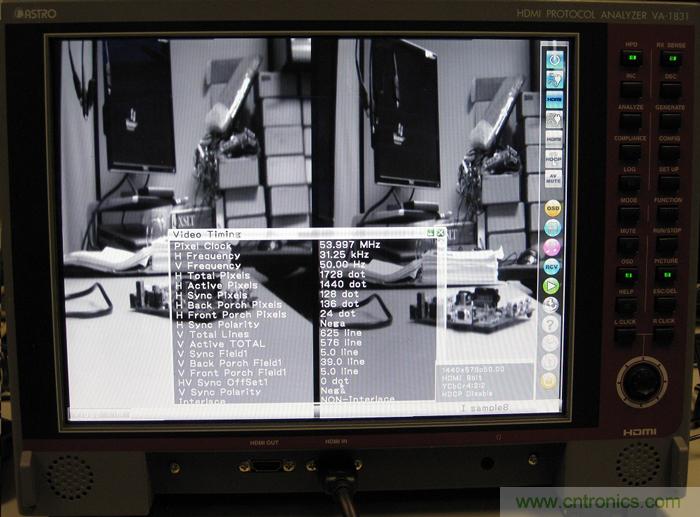

并排3D視頻

對存儲器要求最低的架構(gòu)是并排格式,只需要一個兩行緩沖器(FIFO)即可存儲來自兩個視頻源的行內(nèi)容。并排格式的寬度應(yīng)為原始輸入模式的兩倍。為此,應(yīng)使用一個雙倍時鐘來為擁有雙倍水平行長度的再生同步時序提供時鐘。用于為后端提供時鐘的雙倍時鐘將以雙倍速率清空第一個FIFO和第二個FIFO,這樣即可并排顯示圖像,如圖14所示。并排圖像如圖15所示。

圖14 使用簡單的FPGA行緩沖器來并排合并兩幅圖像

圖15 視頻時序下的并排576p圖像

結(jié)論

ADI公司的解碼器和HDMI產(chǎn)品以及簡單的后處理技術(shù)可以打造出真正的立體3D視頻,并為其傳輸提供條件。如本文所示,用簡單的數(shù)字模塊,無需使用昂貴的存儲器,即可實現(xiàn)3D視頻。這種系統(tǒng)可用于需要3D視覺的任何類型的系統(tǒng)中,從簡單的攝像機(jī),到基于ADSP-BF609 DSP的可以跟蹤物體及其距離的專業(yè)系統(tǒng)。

推薦閱讀: