【導讀】本文主要是提出了一種在后仿真流程中基于芯禾科技高速仿真工具對PCB中無源結構進行快速驗證及優(yōu)化的方法,可以極大地提高工作效率。

一 前言

針對已完成布線的PCB,設計者一方面需要對已完成的關鍵網絡進行仿真驗證,查看實際布局布線是否滿足設計要求;另一方面需要對不滿足要求的結構進行優(yōu)化,然后對改動后的PCB再次進行仿真驗證,確認改動對高速信號帶來的影響。芯禾科技Hermes SI可以快速實現后仿真中對關鍵網絡信號進行仿真驗證的工作,ViaExpert可以便捷地實現對阻抗不連續(xù)處進行快速優(yōu)化,比如過孔、電容焊盤、金手指區(qū)域等,TmlExpert可以便捷地對傳輸線進行建模優(yōu)化,比如帶狀線、微帶線及波導結構等,SnpExpert可以便捷地查看S參數及TDR曲線。

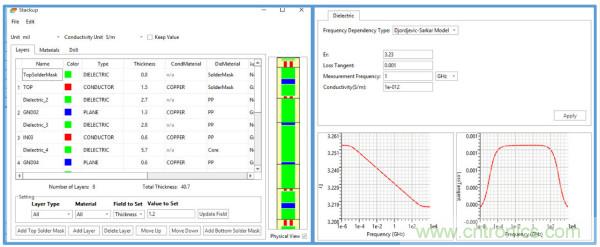

二 設置堆疊及材料信息

依據板廠提供的疊構及材料信息在芯禾科技高速仿真工具中設置堆疊,或者在Cadence Allegro里將堆疊設置正確后,通過Hermes與ViaExpert導入Layout文件后,直接解析獲取堆疊信息。在芯禾科技高速仿真工具中,已支持介質的單頻點與多頻點頻變模型。本文仿真使用的Djordjecvic-Sarkar模型,根據板廠提供的@1GHz的Dk與Df信息設置仿真參數。Layout工程師已按照板廠建議的差分線100ohm阻抗要求的線寬與間距布線。下面通過導入Layout文件進行仿真驗證當前設計是否滿足阻抗要求,若不滿足,則需進一步優(yōu)化。

圖1 設置堆疊與材料信息

三 仿真驗證關鍵網絡的阻抗

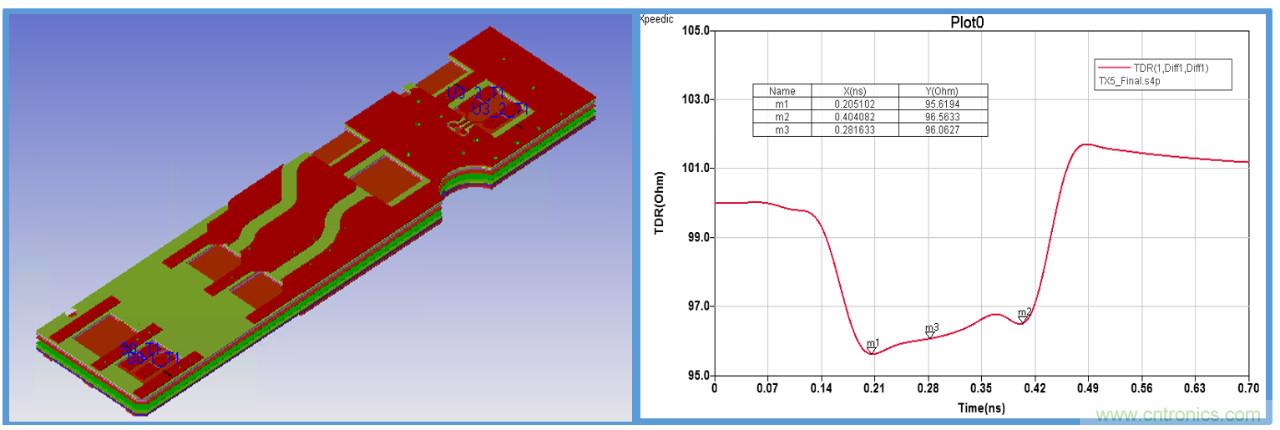

由于當前Layout設計中的關鍵網絡布局一致性較好,可以取具有代表性的網絡進行仿真驗證??紤]到最壞情況下的結果,選擇了走線最長、結構較復雜的網絡。由Hermes SI提取關鍵網絡的整個通道的S參數,掃頻到20GHz,然后通過SnpExpert查看此通道的TDR特性。

圖2是截取的差分對1的模型及TDR結果,此模型是內層走線,兩端是金手指。從TDR曲線可以看出,m1=95.6Ohm與m2=96.6Ohm是對應左右兩端金手指處的阻抗,m3=96Ohm是對應內層走線的阻抗。由此可知,此差分對中,金手指及內層走線阻抗在合理范圍,暫不優(yōu)化。

圖2差分對1的模型及TDR結果

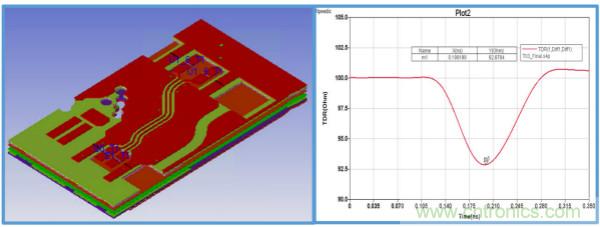

圖3是截取的差分對2的模型及TDR結果,此模型是表層走線,兩端是金手指。由于表層走線較短,且僅掃頻到20GHz,從TDR曲線僅可以看出,最低點是m1=92.9Ohm,但無法嚴格區(qū)分出左右金手指與走線的阻抗??紤]到此處金手指模型跟差分對1處的是一致的,其阻抗不會掉落那么嚴重,又通過ViaExpert單獨仿真金手指處的阻抗,如圖4所示,m1=96.9Ohm。因此造成阻抗掉落的原因極大的可能是走線的阻抗與金手指處阻抗不匹配造成的反射,所以需要對表層走線阻抗做進一步檢查與優(yōu)化。

圖3 差分對2的模型及TDR結果

圖4 金手指處FootPrint、3D模型及TDR結果

四 優(yōu)化不連續(xù)結構的阻抗

4.1優(yōu)化表層走線阻抗

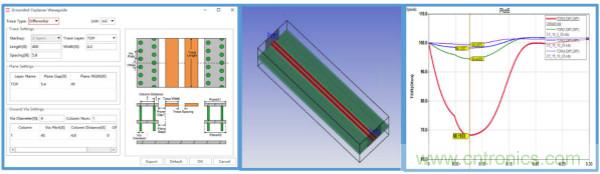

檢查當前Layout文件發(fā)現,表層走線阻抗與板廠聲稱100Ohm阻抗偏差較大的原因是板廠計算阻抗時使用的是微帶線的結構,而當前Layout實際走線是GCPW(Grounded Coplanar Waveguide),所以需要根據當前表層實際走線重新建模優(yōu)化。TmlExpert提供了GCPW的模板,根據當前Layout的參數在不改變過孔布局的前提下,微調線寬、間距及信號對地間距進行優(yōu)化,最終得到滿足阻抗要求的設置,如圖5所示。

圖5 GCPW模板、3D模型及結果對比

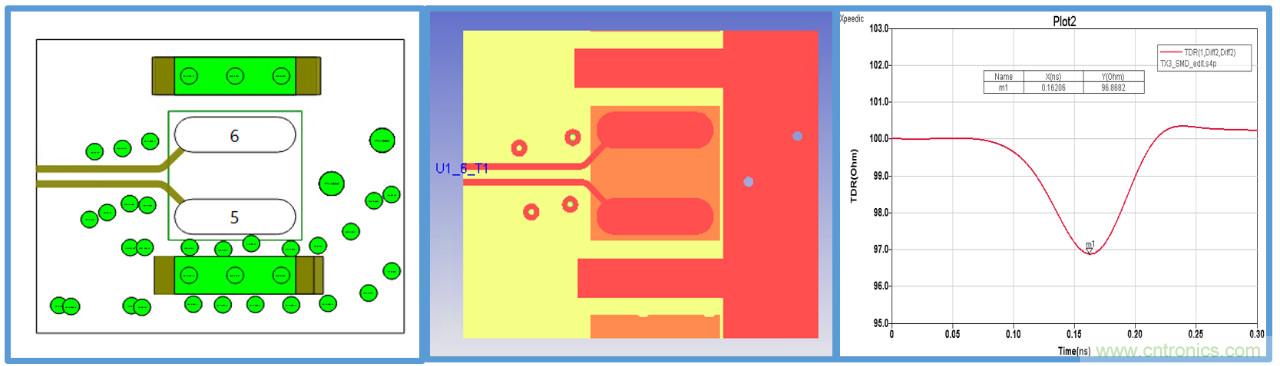

4.2優(yōu)化電容處的阻抗

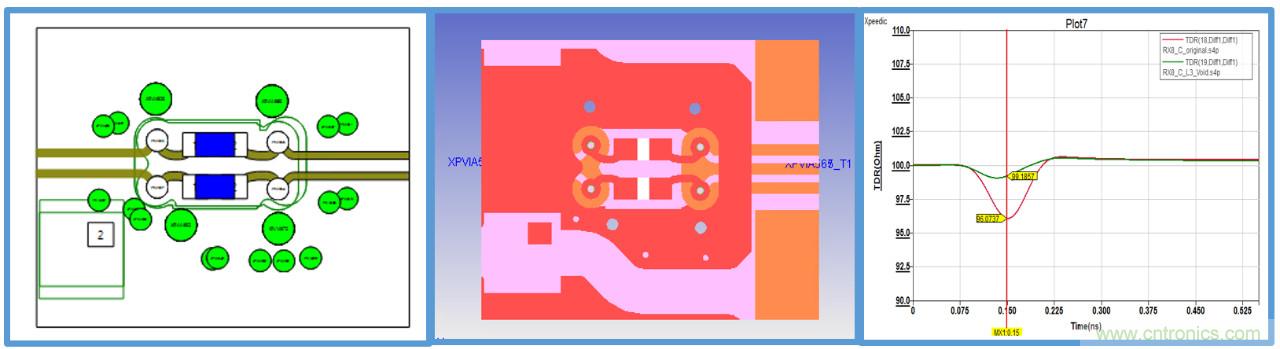

由于當前Layout布局已定,需采取微調的措施,所以嘗試通過挖空相鄰層或者是擴大挖空區(qū)域改變回流路徑方式進行優(yōu)化。ViaExpert可以導入Layout文件,截取模型后,在2D界面添加Keepout方式快速挖空相鄰層或是改變挖空區(qū)域。

在ViaExpert中,對于電容模型,軟件支持在2D界面添加集總的RLC參數。圖6是電容處FootPrint、3D模型及結果對比。TDR結果對比中,紅色是原始挖空區(qū)域的結果,綠色是多挖空一層相鄰層的結果,由此可看出,通過多挖空一層相鄰層就可以改善阻抗,使其達到目標阻抗100Ohm的要求。

圖6 電容處FootPrint、3D模型及TDR結果對比

五 總結

本文使用芯禾科技高速仿真工具完成了后仿真中對PCB無源鏈路的S參數提取及阻抗驗證,并對鏈路中阻抗不連續(xù)的處的走線及電容進行了優(yōu)化。后續(xù)需對改動后的PCB做進一步的驗證,確認改動對阻抗帶來的影響。

本文轉載自芯禾科技。

推薦閱讀: