【導讀】通用串行總線(USB)規(guī)范的3.0版本提供了比USB2.0在性能上的飛躍。將數(shù)據(jù)速率提高了10倍。它還將傳輸線擴展到3個差分對(與前2.0代中的1個相比)。USB于1996年推出1.0版。在低速度(LS)模式下1.5Mbit/sec,在全速度(FS)模式下12Mbit/秒。在2000年USB2.0進入市場。新的高速(HS)模式可達480Mbit/sec。它仍然向下兼容低速和全速模式。

USB3.0特點

通用串行總線(USB)規(guī)范的3.0版本提供了比USB2.0在性能上的飛躍。將數(shù)據(jù)速率提高了10倍。它還將傳輸線擴展到3個差分對(與前2.0代中的1個相比)。USB于1996年推出1.0版。在低速度(LS)模式下1.5Mbit/sec,在全速度(FS)模式下12Mbit/秒。在2000年USB2.0進入市場。新的高速(HS)模式可達480Mbit/sec。它仍然向下兼容低速和全速模式。

目前,USB2.0是最廣泛、最通用的外部數(shù)據(jù)接口之一。已成為所有計算機系統(tǒng)的默認標準接口。

USB2.0接口也廣泛應用于消費電子產(chǎn)品。比如便攜式攝像機、數(shù)碼相機、數(shù)碼音樂播放器、游戲機、DVD/藍光播放器和電視等設備都使用USB。它也廣泛應用于便攜式設備,如智能手機和網(wǎng)絡設備如DSL/路由器單元。

靜電保護設計考慮

對于整個USB3.0鏈接,以下設計考慮應注意:

以下強制性的。

• 非微分耦合線必須最小化。它們對眼圖有重要的影響。

• 90歐姆差別的線寬和線距:耦合的PCB道不應太窄,以避免額外的損失,并在制造時要足夠堅固。差動道之間的線寬0.007"(0.178mm)和線距0.007"(0.178mm)是在生產(chǎn)時最佳的選擇。

• 微分耦合連接(減少對斜)的正負線(包括USB3.0電纜)之間的相同延遲(線長)是需要的。這對于保持高信號完整性和避免共模反射是很重要的。

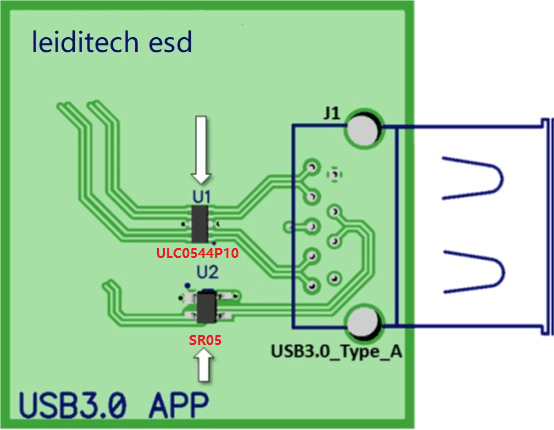

圖1展示了USB3.0標準-A連接器部分與ESD保護器件相結合的布局圖例

上圖中,采用雷卯的ULC0544P10保護保護SuperSpeed的TX和RX數(shù)據(jù)對。

SR05封裝SOT-143保護USB2.0線對D+和D-,同時SR05內部有一個瞬態(tài)電壓抑制器(TVS)保護VBUS。ULC0544P10有4條超低線接地,電容為0.3pF,保護USB高速信號完整性。

ESD的小型化需求

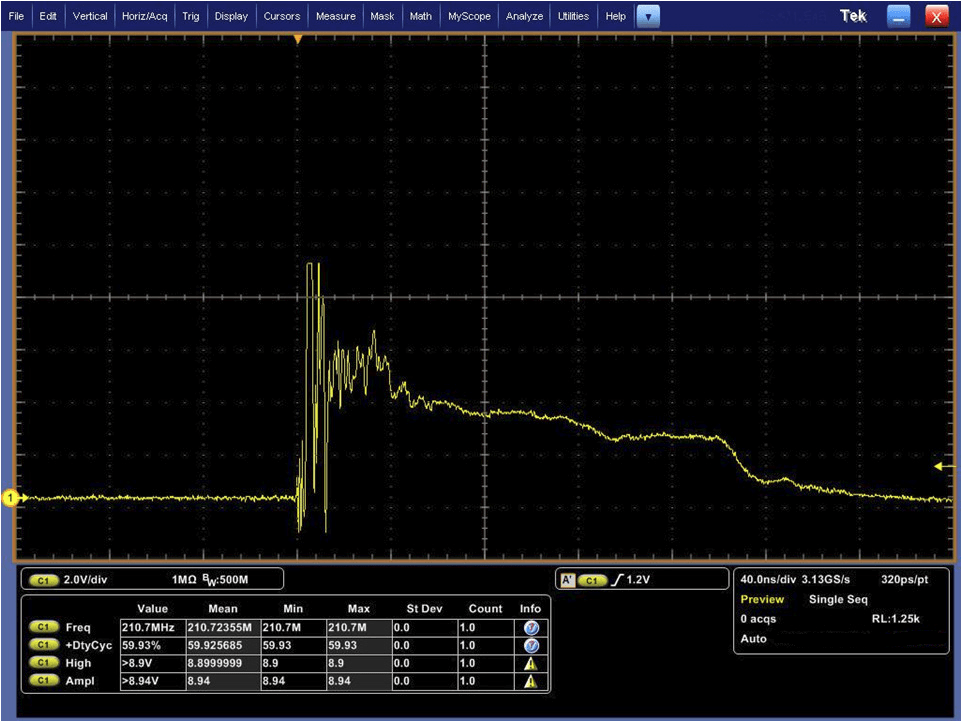

ESD保護器件的小型化帶來了額外的問題。和較大的模具相比要更高的鉗位和低的穩(wěn)健性。雷卯電子的新芯片設計緩解了這一問題。根據(jù)IEC61000-4-2,ULC0544P10箝位8kV接觸放電,是一個很低的6V的鉗位電壓在30nSec點測量。如圖2所示。對于-8KVESD放電鉗位通常是一個二極管壓降(1.2V)接地。單向二極管直接傳導到地。

圖2:+8kV接觸放電IEC61000-4-2。

眼圖

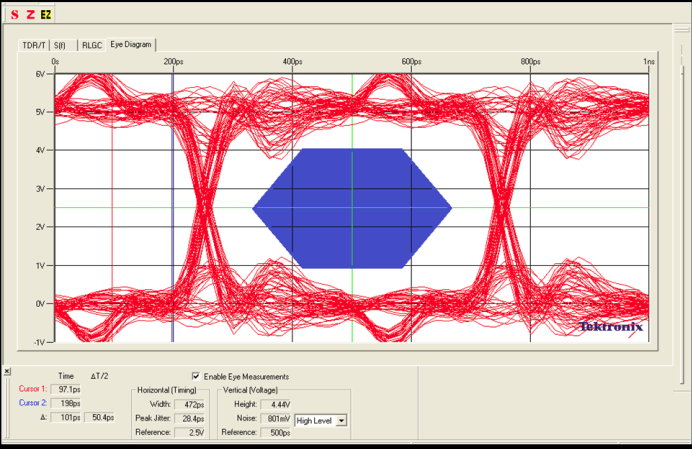

圖3:USB3.0的眼圖(ULC0544P10)。

由上面眼圖可知,線路電容對眼罩的影響很小。超高速數(shù)據(jù)傳輸系統(tǒng)存在嚴重的設計障礙。設計必須確保接收機一定程度的信號完整性。高信號完整性對實現(xiàn)低誤碼率是很重要的(例對于USB3.0Superspeed,1E-12的誤碼率是典型的)。信號完整性其特點如上述眼圖。

在一個不受帶寬限制的完美系統(tǒng)中,眼圖將是完全開放的。在實際系統(tǒng)中,信號上升時間/下降時間受到TX和RX阻抗(90歐姆差分)的限制)。這與TX側和RX側的所有寄生電容相結合。這些寄生電容在USB3.0收發(fā)器內,和/或在PCB外部。外部可能是由不匹配的PCB線、USB3.0連接器或其他并聯(lián)電容器引起的。并聯(lián)電容器的數(shù)值應盡可能小。USB3.0電纜的低通頻率響應也必須考慮在內。為了補償頻率的衰減,信號通過TX和RX的專用均衡來調諧。

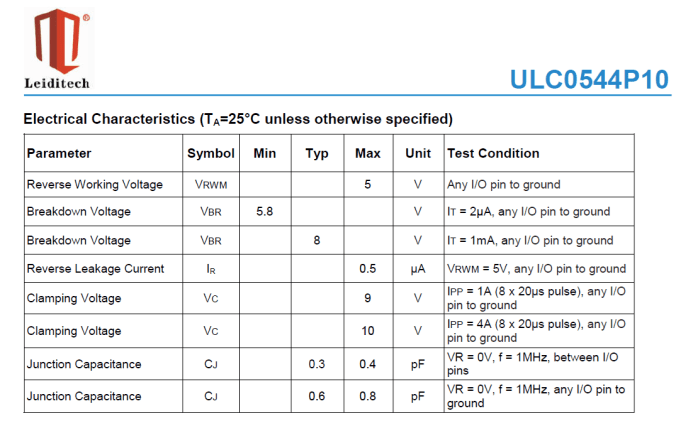

規(guī)格書

以下是ULC0544P10的規(guī)格書部分內容,可以看到低鉗位的特性。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。

推薦閱讀: