【導讀】在半導體行業(yè)中,“微縮(Scaling)”是一個經(jīng)常出現(xiàn)的詞語,比方說,我們經(jīng)常在半導體行業(yè)的新聞中聽到有關(guān)晶體管微縮(即把納米級(Nano-scale)的尺寸縮小至原子級別)的信息。

在半導體行業(yè)中,“微縮(Scaling)”是一個經(jīng)常出現(xiàn)的詞語,比方說,我們經(jīng)常在半導體行業(yè)的新聞中聽到有關(guān)晶體管微縮(即把納米級(Nano-scale)的尺寸縮小至原子級別)的信息。或者,我們又曾聽說過,我們?nèi)粘J褂玫闹悄苁謾C等電子設備由于采用了容量較大(Scaling)的存儲半導體,因此能夠存儲清晰度較高的視頻。無論什么樣的新聞,基本都意味著微縮(Scaling)的進步。

以上這些進步都是由元件接觸面積(Footprint)的縮小、三維結(jié)構(gòu)的擴大、新材料和革新結(jié)構(gòu)的采用所帶來的效果。如今的數(shù)字時代因以上這些技術(shù)的發(fā)展和進步而得以成立。如今,使我們的日常生活發(fā)生翻天覆地變化的電子設備是由于微縮(Scaling)而得以誕生的,而且,今天的我們只需動動手指就可以獲得海量的數(shù)字信息。

晶體管的微縮(Scaling)

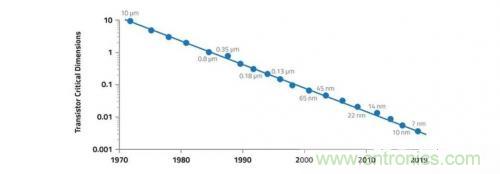

就半導體的微縮(Scaling)而言,摩爾定律是眾所周知的。即當價格不變時,集成電路上可容納的元器件的數(shù)目每隔 18 個 -24 個月便會增加一倍,性能也將提升一倍。

最近幾十年來,隨著光刻(Lithography,在晶圓表面影印成線路圖案的加工技術(shù))和等離子蝕刻(Plasma Etching)技術(shù)的進步,半導體行業(yè)正在逐步縮小晶體管這一重要的(或者說是不可或缺的)構(gòu)成要素,且獲得了較大的發(fā)展。

此外,就半導體的技術(shù)節(jié)點(Technology Node)而言,一般指的是晶體管的閘極(Gate)的長度。比方說,所謂 0.5um 的技術(shù)節(jié)點指的就是閘極(Gate)長度為 0.5um 的晶體管。但是,隨著時代的發(fā)展,技術(shù)節(jié)點的定義也在變化,如今不再是晶體管相關(guān)的主要部分的尺寸指標,而僅是指代元件的代際的名稱。但是,隨著節(jié)點的微縮發(fā)展,人們對于提高元件的性能和功率、削減生產(chǎn)成本的目標從來沒有改變過。

圖片出自:mynavi)

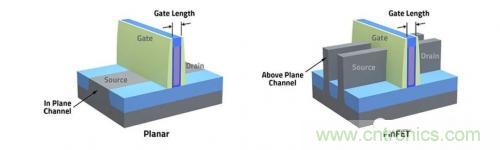

高性能晶體管在 20nm 節(jié)點前后達到了微縮的極限。半導體行業(yè)的工程師們不得不探索其他設計晶體管的方法,因為如果縮小平面型(Planar)晶體管的水平尺寸,將會產(chǎn)生其他問題。

就三維 FinFET(鰭式場效應晶體管)的結(jié)構(gòu)而言,晶體管的主要構(gòu)成要素相對于硅晶圓而言較立體,因此不會減少晶體管的溝道(Channel)的容量,而是縮小元件的接觸面積(Footprint)。就 FinFET 的微縮而言,作為提高元件性能的方法,一般是在提高 Fin 的高度的同時,為提高每個單元(Unit)面積的元件密度而縮小水平尺寸。

為了維持晶體管的微縮,以及獲得高性能、低功耗、低成本的元件,近年來實施的方法是往硅里添加鍺(Germanium),但要用 FinFET 技術(shù)超越 5nm 的節(jié)點,還是需要新材料!此外,壓層納米板(Nano Sheet)、納米線(Nano Wire)等新的材料很有可能成為新的解決方案。要對這些新材料進行加工,毫無疑問,微縮是必須的,且靈活運用原子層級別的成膜以及蝕刻工藝都是必須的。

(圖片出自:mynavi)

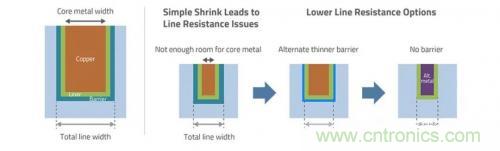

接觸(Contact)層的微縮(Scaling)

如果縮小晶體管的尺寸,為了連接晶體管、排線層,就需要整體縮小接觸(Contact)層的尺寸。隨著代際的進步以及局部內(nèi)部聯(lián)系(Inter-connect)的密度越來越高,如果進一步推進微縮的發(fā)展,如今主流的銅配線將會面臨嚴重的課題。比方說,如果要進一步降低配線的寬幅、高度,則銅配線的電阻將會大幅度增高。半導體生產(chǎn)廠家在靈活運用既能防止銅污染又具有較高電阻值的新阻擋(Barrier)材料、新襯墊(Liner)材料的同時,力求減小阻擋(Barrier)層、襯墊(Liner)層的空間。另一種可能性是使用一種不需要阻擋(Barrier)層的其他金屬來取代銅,或者使用其他金屬與銅的合金。

(圖片出自:mynavi)

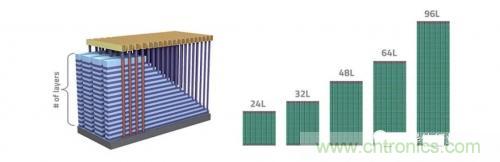

存儲半導體容量的微縮(Scaling)-- 即容量的擴大

3D NAND 的存儲半導體容量的微縮(Scaling)是通過垂直方向的堆疊來實現(xiàn)的。就存儲半導體的結(jié)構(gòu)而言,單元(Cell)密度與堆疊層的層數(shù)成比例地增加。初期的 3D NAND 一般采用的是 24 層構(gòu)造的芯片,如今 96 層、128 層構(gòu)造的芯片已經(jīng)量產(chǎn),因此預計堆疊層數(shù)將會進一步增加。而且,每一層都需要均勻、光滑,且與下層緊密結(jié)合,因此堆疊層數(shù)帶來的課題也增加了。

堆疊層數(shù)的持續(xù)增加帶來了存儲半導體容量的擴大,而存儲半導體容量的擴大又使具有較高縱深比(Aspect)的存儲孔(Memory Hole)的蝕刻、階梯(Staircase)圖形的定義、字線(Word-line)的鎢填充等后續(xù)工藝更加復雜。此外,如果溝道(Channel)長度變長,電子遷移率會受到限制,影響設備的性能。眼下,人們正在推進運用重要的成膜工藝以及蝕刻工藝來切實推進新代際的發(fā)展。

(圖片出自:mynavi)

匯總

如今最尖端的芯片毫無疑問是迄今為止設計、生產(chǎn)的產(chǎn)品中最先進的元件,也是歷經(jīng)幾十年人們推進微縮的直接成果。今天的縮小水平方向尺寸的、謀求縱向堆疊的元件所要求的性能(Performance)和成本(Cost)優(yōu)勢會因為半導體生產(chǎn)設備的進步、生產(chǎn)設備廠家和芯片廠家的強化合作而得以實現(xiàn)。

通過半導體的微縮(Scaling)發(fā)展,我們的工作、通勤、娛樂、通信方式獲得了翻天覆地的變化。作為改革(Innovation)的方向性,我們期待“More Moore(延續(xù)摩爾定律)”可以持續(xù)下去。作為支撐半導體行業(yè)得以發(fā)展的另一個方向性—-- 將各種各樣的技術(shù)融合到各種各樣的構(gòu)造、系統(tǒng)中的“More than Moore(新摩爾定律、超越摩爾定律)”戰(zhàn)略也頗受矚目。

未來,我們需要同時推進以上這兩個方向的進步,但是,要推進實現(xiàn)更智能(Smart)、更互聯(lián)(Connected)的社會而必須的速度和性能需要被應用到更多的行業(yè)和領中。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進行處理。