【導(dǎo)讀】當(dāng)今的模數(shù)轉(zhuǎn)換器 (ADC) 采用了最新的技術(shù),以高精度及快速的采樣頻率對(duì)模擬信號(hào)進(jìn)行采集。數(shù)據(jù)轉(zhuǎn)換器的復(fù)雜性隨著采樣頻率及精度的提高而增加。高性能數(shù)據(jù)轉(zhuǎn)換器規(guī)格的設(shè)定必須遵循嚴(yán)格的輸入條件,以實(shí)現(xiàn)器件預(yù)期性能的最大化。

當(dāng)今的模數(shù)轉(zhuǎn)換器 (ADC) 采用了最新的技術(shù),以高精度及快速的采樣頻率對(duì)模擬信號(hào)進(jìn)行采集。數(shù)據(jù)轉(zhuǎn)換器的復(fù)雜性隨著采樣頻率及精度的提高而增加。高性能數(shù)據(jù)轉(zhuǎn)換器規(guī)格的設(shè)定必須遵循嚴(yán)格的輸入條件,以實(shí)現(xiàn)器件預(yù)期性能的最大化。一個(gè)頗具挑戰(zhàn)性的輸入條件是:對(duì)ADC輸入模擬信號(hào)進(jìn)行測(cè)量、驅(qū)動(dòng)和接口連接。本文將探討一些對(duì)于高速 ADC進(jìn)行有效接口連接的技術(shù),從而使ADC實(shí)現(xiàn)性能最佳化。

就有效輸入驅(qū)動(dòng)以維護(hù)信號(hào)完整性而言,已經(jīng)有許多好的應(yīng)用注釋以及文章發(fā)表。本文將探討有關(guān)輸入驅(qū)動(dòng)的新發(fā)展。

ADC 輸入架構(gòu)與驅(qū)動(dòng)器的選擇

ADC的模擬輸入配置隨著采樣精度和最大采樣頻率的變化而有所不同。在輸入階段,影響輸入驅(qū)動(dòng)器選擇的特征有:

1. 單端與差分

2. 高阻抗與低阻抗 (100W) (或是有緩沖與無(wú)緩沖)

單端與差分

大部分推動(dòng)采樣精度和采樣頻率達(dá)到極限的ADC采用的是差分輸入方式。差分輸入的優(yōu)勢(shì)在于降低偶次諧波和 EMI。一些差分輸入ADC具有IRS(輸入范圍選擇) 寄存器,其允許使用者通過(guò)將未使用的輸入連接到共模 (CM)A/D轉(zhuǎn)換參照的方式,以單端輸入來(lái)使用器件。

有緩沖與無(wú)緩沖

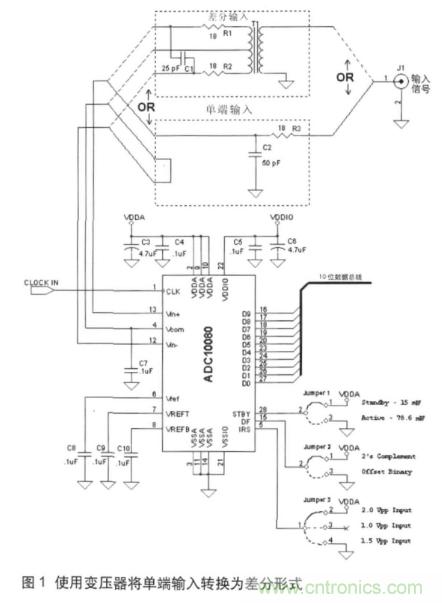

高采樣頻率ADC (》500 MSPS) 經(jīng)常要處理高頻模擬輸入信號(hào)。假定使用標(biāo)準(zhǔn)的 PCB板尺寸和軌跡長(zhǎng)度,如果這個(gè)高頻模擬信號(hào)沒(méi)有正常結(jié)束,又用處理射頻信號(hào)和電路板的方式加以處理,模擬信號(hào)就會(huì)衰退。這樣的高頻應(yīng)用得益于低阻抗 (50W單端或 100W差分) 模擬輸入,因此,大部分 UHF 和 VHF 電路為 50W系統(tǒng)。為了獲得較高的失真性能,通常使用差分輸入。由于嚴(yán)格的規(guī)范限制,以及受高頻的影響,高采樣率ADC通常不提供允許使用單端輸入的IRS 選項(xiàng)。原因是:采用 IRS 的ADC需要額外的電路才能轉(zhuǎn)換到滿量程(FSR),而這對(duì)于在高頻/高采樣率下的應(yīng)用卻并不可行。因此,這個(gè)等級(jí)的ADC需要高頻、低電阻 (100W差分)的輸入驅(qū)動(dòng)。使用低電阻輸入 ADC,模擬輸入在被應(yīng)用到用于轉(zhuǎn)換的采樣/保持 (S/H) 電路之前就已緩沖。所以,并不需要采用在非緩沖 ADC中使用的標(biāo)準(zhǔn)去耦電路 (串聯(lián)電阻R,并聯(lián)電容C)。在圖1的圖解中使用了一個(gè)非緩沖輸入的 ADC (ADC10080),這些去耦元件在圖中標(biāo)識(shí)為 R1、R2(18W) 及 C1 (25W)。

從單端到差分的轉(zhuǎn)換

中點(diǎn)接線變壓器

(Ruthroff 變壓器)

如前所述,驅(qū)動(dòng)差分 ADC 的輸入必須為差分形式。將單端輸入轉(zhuǎn)換為ADC 可用的差分信號(hào)需要使用一個(gè)中點(diǎn)接線變壓器,如圖1所示(在“差分輸入”虛線下可看出變壓器如何接到 ADC 輸入)。

差分輸入的共模電壓(CM)應(yīng)遵循 VCOM 電壓(在 ADC 上的輸出引腳),以便使 ADC 內(nèi)部的采樣保持電路正常工作。圖1中的電路允許通過(guò)將變壓器的中點(diǎn)接線連接到ADC的 VCOM 輸出來(lái)對(duì)輸入 CM 加以設(shè)定。

變壓器的較低截止頻率不允許低頻內(nèi)容被耦合進(jìn)來(lái)。因此,這種形式的耦合只可應(yīng)用于不需要 DC 以及低頻內(nèi)容的系統(tǒng)。除此之外,這個(gè)電路也承受了高頻變壓器的泄漏效應(yīng),限制了它的上限工作頻率。典型的變壓器有上限及下限工作頻率。較低頻率限制由初級(jí)電感決定。對(duì)于這個(gè)與 8 位轉(zhuǎn)換器一起使用的變壓器而言,如果不采用其它的增益校準(zhǔn)或調(diào)整方法,其工作的頻帶非常窄,受限在 1 MHz ~100MHz,其中,插入損耗變化小于 0.034dB (1 LSB)。

對(duì)于最大回波損耗(最小反射),許多較高速度的應(yīng)用要求對(duì)圖1中 J1 (輸入連接器)處的輸入阻抗進(jìn)行控制,并且要與連接到連接器的電纜特征阻抗相匹配。當(dāng)電纜的長(zhǎng)度超過(guò)所遇最短波長(zhǎng)的 1/20時(shí),這種要求尤為重要。只要變壓器回波損耗在頻率極值時(shí)性能沒(méi)有衰退,就有可能通過(guò)設(shè)置一個(gè)通過(guò)輸入的終端電阻 RT 來(lái)達(dá)成此目標(biāo)。這樣,輸入阻抗就會(huì)接近RT,原因在于變壓器回波損耗已增大,足以具有最小負(fù)載效應(yīng)。在較高的頻率下,由于變壓器回波損耗的減少,使用這種類型的變壓器配置會(huì)使控制輸入端更加困難。而這正是不平衡變壓器的優(yōu)勢(shì)所在。

不平衡變壓器

(Guanella變壓器)

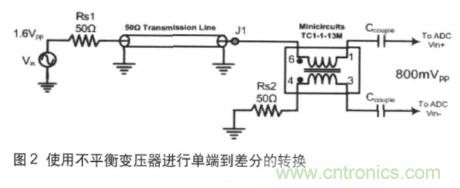

另一個(gè)進(jìn)行單端到差分轉(zhuǎn)換的方法是使用不平衡變壓器,如圖2所示。

與圖1相比,這種方式具有下述優(yōu)點(diǎn)及缺點(diǎn):

優(yōu)點(diǎn):

1. 較高的工作頻率

2. 對(duì)于寬帶應(yīng)用而言,有較高的回波損耗

3. 較佳的增益與相位平衡

缺點(diǎn):

1. 無(wú)法設(shè)定共模電壓

2. 無(wú)法提供電壓增益

與圖1的中點(diǎn)接線變壓器或 Ruthroff 變壓器相比,不平衡配置有著更高的工作頻率。然而,采用不平衡配置后,因?yàn)闊o(wú)法設(shè)定共模電壓水平,ADC 輸入必須為 AC 耦合電壓。以ADC08D1500為例,它是一個(gè) 8 位、1500MSPS 的轉(zhuǎn)換器,如果在 AC耦合的模式下工作,就會(huì)通過(guò)內(nèi)部電阻自動(dòng)將其輸入端偏置到適當(dāng)?shù)墓材k妷褐?。如果ADC的 VCMO 輸出接地,就會(huì)以 AC 耦合模式運(yùn)行。

如圖2所示,使用 AC 耦合電容 (4.7nF),輸入耦合電路的-3dB頻率大約為 677 KHz (=1/(2pReqCeq),其中,Req=100W,Ceq=4.7nF/2=2.35nF)。這個(gè) 100W的等效電阻是耦合電容器 (RT2與 ADC 的 100W輸入并聯(lián),總共 50W) 右邊的差分負(fù)載與介于不平衡變壓器引腳1 和引腳3(50W)間差分阻抗的串聯(lián)組合。

采用圖2的電路,J1終止于 50W 左右,并且假定所驅(qū)動(dòng)的ADC具有100W的差分輸入終端(如 ADC08D1500)。與 100W ADC輸入阻抗并聯(lián)的 RT2為 50W,這是從 J1 到接地的輸入阻抗。此輸入阻抗一直保持一定的頻率,從而使不平衡變壓器發(fā)揮變壓器的作用。超過(guò)這個(gè)基于特殊不平衡變壓器及其核心特征、線圈間電容,以及其它因數(shù)的頻率范圍,輸入阻抗就會(huì)偏離這個(gè)值,并且輸入反射會(huì)導(dǎo)致回波損耗減少。大部分不平衡變壓器的產(chǎn)品手冊(cè)都列出了幾個(gè)頻點(diǎn)的回波損耗與上限和下限工作頻率。

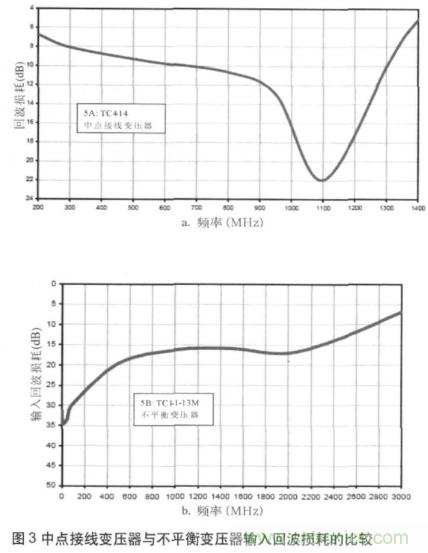

圖3顯示了一個(gè)中點(diǎn)接線變壓器 (TC4-14) 以及一個(gè)不平衡變壓器 (TC1-1-13M) 的輸入回波損耗,并進(jìn)行了簡(jiǎn)單的比較。

由圖3中可以看出,中點(diǎn)接線變壓器的回波損耗在 700MHz 以下與 1.3GHz 以上時(shí),下降得十分迅速,而不平衡變壓器則具有一定的高出數(shù) MHz 的回波損耗 (》 10dB),并且在頻率到達(dá)約 2.6GHz 左右時(shí)才開始下降。這是不平衡變壓器相對(duì)于中點(diǎn)接線變壓器的優(yōu)點(diǎn)。在較高頻率減少的回波損耗會(huì)造成一種不匹配的狀態(tài),并且產(chǎn)生較高的反射能量,這會(huì)在采集信號(hào)中形成不想要的諧波,并且降低系統(tǒng)的 ENOB 性能。

回波損耗 (RL)與 二端口輸入阻抗相關(guān),如式1如示:

RL= 20 Log | (Zin+50)/ (Zin-50)| (1)

舉例來(lái)說(shuō),10dB 的 RL 與96W 或 26W的輸入阻抗相符合 (根據(jù)式1中商的符號(hào)而定)。阻抗不連續(xù)時(shí)的反射波(圖2中的 J1)在源端出來(lái)另一個(gè)反射之后將會(huì)抵達(dá) Rs1 (假定來(lái)源與傳輸線并沒(méi)有完美匹配)。往返時(shí)間為 l/n,其中,l為電纜長(zhǎng)度,n為通過(guò)傳輸線介質(zhì)的波速。構(gòu)成輸入信號(hào)的不同頻率元件,在遇到此往返延遲并且加上原來(lái)的入射波之后會(huì)回到中斷處,從而形成最終的信號(hào)。對(duì)于往返延遲 (2l/n),l為一個(gè)重要的諧波(大約是周期 T 的 1/10),其最終的波形將會(huì)失真。從數(shù)學(xué)上講,這里的T滿足了 T ≤ (20 l/n) 的諧波要求。原因是,對(duì)于較短周期的諧波,入射以及反射波會(huì)合成(在時(shí)間上)交迭形式,這會(huì)造成波形的改變。這正是在 ENOB 上降低的原因,因?yàn)檫@個(gè)改變的波形將會(huì)增加總諧波失真 (THD) 的失真項(xiàng),從而產(chǎn)生較低的 ENOB。

為了平衡非平衡功能,變壓器的初級(jí)與次級(jí)總會(huì)保持1:1 的比例,因此,此配置不能提供任何電壓增益。

有源單端到差分的轉(zhuǎn)換

如前所述,變壓器可以被用作轉(zhuǎn)換器,然而它們?cè)趯拵У膽?yīng)用上有很大的缺點(diǎn),并且在這些應(yīng)用中,它們不會(huì)在其操作頻率區(qū)域中包括 DC 和低頻?;谶@個(gè)原因,半導(dǎo)體制造商已經(jīng)導(dǎo)入了有源器件來(lái)執(zhí)行這項(xiàng)功能,以彌補(bǔ)變壓器耦合結(jié)構(gòu)的缺點(diǎn)。

LMH6555 是專門設(shè)計(jì)用來(lái)驅(qū)動(dòng)如圖4顯示為 0.8Vpp的ADC的 100W差分輸入,并且提供一個(gè)到終端電纜的固定 50W的輸入阻抗(未顯示于圖4中),以達(dá)到最高的回波損耗。單端到差分轉(zhuǎn)換器會(huì)將頻率范圍從DC一直擴(kuò)展到1.2GHz(此為 LMH6555 的 -3dB 頻寬限制)。通過(guò)將ADC的 VCMO連接到 LMH6555 的 VCM_REF 輸入,可以保持精確的輸出共模電壓控制。利用這樣的結(jié)構(gòu),可以獲得全信號(hào)頻譜,而共??刂苿t可以由 LMH6555 自動(dòng)實(shí)現(xiàn)。圖4中所示的緩沖器 (LMV321) 用來(lái)提高ADC的 VCMO 引腳所流出的電流,以使得對(duì)于 VCM_REF輸入而言有適當(dāng)?shù)尿?qū)動(dòng)能力。是否需要緩沖器取決于ADC的電流輸出能力?! ?/span>

LMH6555 的增益(在Vin+下的差分輸出到單端或取決于所驅(qū)動(dòng)輸入的Vin+)確定在 4.8V/V,其配置如圖4所示,其中,Rs1=Rs2=50W。對(duì)于輸入信號(hào)在振幅上較大的情形,LMH6555 插入增益可以通過(guò)增加 Rs2和 Rs1的值來(lái)降低。這兩個(gè)電阻應(yīng)該總是相等,以保持對(duì)于低輸出偏移的輸入平衡。圖5所示例子中,位于 50W電纜接收端的 LMH6555 的增益通過(guò) Rx 和 Ry降低。通過(guò)選擇組件值,LMH6555 電路(J1)的輸入阻抗被保持在50W,以使阻抗匹配。兩個(gè) LMH6555具有 100W的到地等效阻抗,各個(gè)組成值都被顯示,以用來(lái)維持低輸出偏移電壓。LMH6555的輸入/輸出擺幅關(guān)系如式2所示:

Vout (Vpp) = Vin (Vpp) * [ RF/ (2Rs+Rin_diff)] (2)

其中,RF= 430W,Rin_diff=78W,都是LMH6555 特定的值。

Rs是等效電阻,使 LMH6555 的輸入接地(假定它們相等)。增加 Rs會(huì)降低增益。重新整理式2,允許使用者決定 Rs的值,可以確定對(duì)于一個(gè)給定 Vin (Vpp) 的全ADC的輸入擺幅,如式3所示:

Rs=Vin (Vpp) * 268.8 - 39 (3)

LMH6555的等效輸入電阻通過(guò) Rs被增加到100W(由式3計(jì)算得出),因此,0.52Vpp輸入會(huì)導(dǎo)致ADC輸入恰好為 0.8Vpp,而J1的等效輸入則維持在 50W。

LMH6555將維持低噪聲 (參照19nV/RtHz輸出的平帶),并與它輸入的Rs無(wú)關(guān)。這是因?yàn)?LMH6555 的輸入架構(gòu)由等效輸入噪聲電壓決定,并且獨(dú)立于源電阻。

ADC要求差分輸入的共模電壓(在 +/-50mV內(nèi))非常接近它所產(chǎn)生的 VCMO 參考輸出。這是采用1.9V供電電壓的一個(gè)結(jié)果,因?yàn)閾p失的供電電壓降低了ADC內(nèi)部的電壓余量。如果未能保持此共模操作,ADC的全失真性能將會(huì)迅速惡化。

除了這種共?,F(xiàn)象外,ADC兩個(gè)輸入端的任何增益和相位不平衡都會(huì)導(dǎo)致獲取錯(cuò)誤信號(hào)。舉例來(lái)說(shuō),一個(gè) 100MHz的方波將會(huì)在它的尖峰值有 1.5% 的錯(cuò)誤。8 位數(shù)據(jù)采集具有全尺度 0.39% 的 LSB,并且不平衡變壓器等效于3.8LSB。所以,將增益和相位不平衡最小化是非常必要的。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問(wèn)題,請(qǐng)聯(lián)系小編進(jìn)行處理。