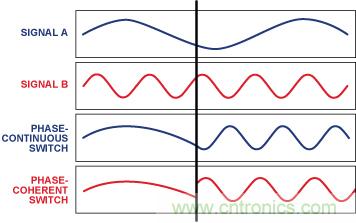

【導(dǎo)讀】常見的單通道直接數(shù)字頻率合成器(DDS)可產(chǎn)生如圖1所示的相位連續(xù)頻率轉(zhuǎn)換。但在相干脈沖多普勒雷達(dá)和用于醫(yī)療和材料分析的NMR/MRI波譜等應(yīng)用中,相位相干轉(zhuǎn)換是首選。本文說明如何配置AD9958/AD9959多通道DDS,通過疊加DDS輸出實(shí)現(xiàn)穩(wěn)定的相位相干頻移鍵控(FSK)調(diào)制器。

多通道DDS幾乎完全消除了同步多個(gè)單通道器件時(shí)遇到的通道間溫度和時(shí)序問題。多通道DDS輸出盡管相互獨(dú)立,但可共用同一系統(tǒng)時(shí)鐘,因此對溫度和電源偏差的追蹤性能優(yōu)于多個(gè)單通道器件的輸出。所以,多通道DDS更適合在疊加輸出端產(chǎn)生相位相干頻率轉(zhuǎn)換。

圖1. 相位連續(xù)和相位相干頻率轉(zhuǎn)換。

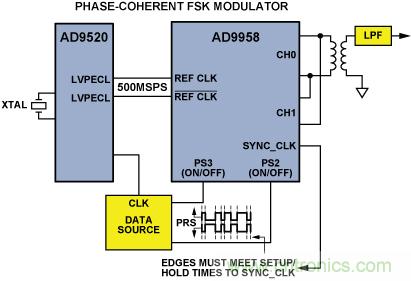

電路描述

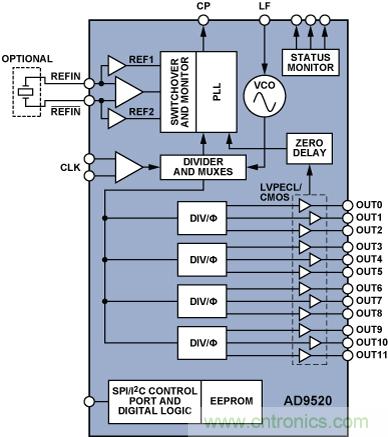

AD9520 時(shí)鐘分配器件通過高性能基準(zhǔn)時(shí)鐘驅(qū)動(dòng)AD9958 DDS,同時(shí)為FSK數(shù)據(jù)流源提供相同時(shí)鐘。AD9520提供多種輸出邏輯選擇和可調(diào)延遲,以滿足FSK數(shù)據(jù)流與多通道DDS SYNC_CLK間的建立和保持時(shí)間。

AD9958的兩個(gè)獨(dú)立通道采用預(yù)編程頻率F1和F2工作。將輸出端連接在一起進(jìn)行疊加。模式(Profile)引腳驅(qū)動(dòng)各DAC輸入的乘法器以控制輸出幅度,這些引腳可開啟或關(guān)閉通道輸出以選擇理想頻率。為此,每個(gè)乘法器預(yù)編程兩個(gè)模式可選設(shè)置:零電平和滿量程。模式引腳上的邏輯低電平將關(guān)閉正弦波,而邏輯高電平將其傳遞至輸出端。該操作需要兩個(gè)互補(bǔ)輸入數(shù)據(jù)流以在頻率間交替。請注意,兩個(gè)DDS通道持續(xù)產(chǎn)生頻率 F1和F2。關(guān)閉功能將消除相應(yīng)的DDS輸出,從而產(chǎn)生相位相干FSK信號。

圖2. 相位相干FSK調(diào)制器設(shè)置。

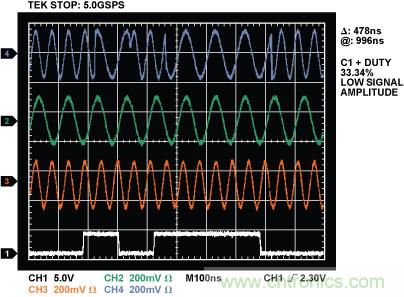

AD9959 4通道DDS產(chǎn)生如圖3所示的結(jié)果。兩個(gè)額外通道可用作疊加輸出端兩個(gè)開關(guān)頻率的相位基準(zhǔn),以便于說明相位相干開關(guān)。上面的波形顯示的疊加輸出表示相位相干開關(guān)。中間兩條波形顯示的是基準(zhǔn)信號F1和F2。下面的波形顯示的是在兩個(gè)頻率間交替的偽隨機(jī)序列(PRS)數(shù)據(jù)流。請注意,由于器件內(nèi)的流水線延遲,PRS數(shù)據(jù)流邊沿與疊加輸出的頻率轉(zhuǎn)換并未完全對準(zhǔn)。

圖3. 實(shí)測的相位相干FSK轉(zhuǎn)換。

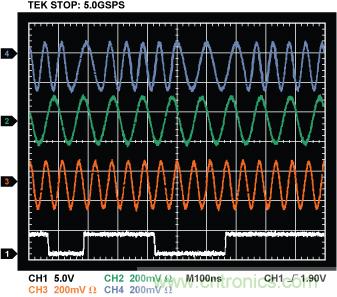

圖4顯示了同樣由AD9959產(chǎn)生的相位連續(xù)FSK開關(guān)的一個(gè)范例。這種操作需要的帶寬較少,但轉(zhuǎn)換之間無相位存儲。

圖4. 實(shí)測的相位連續(xù)FSK轉(zhuǎn)換。

ADI公司提供各種直接數(shù)字頻率合成器、時(shí)鐘分配芯片和時(shí)鐘緩沖器,用來構(gòu)建基于DDS的時(shí)鐘發(fā)生器。如需了解更多信息,請?jiān)L問www.analog.com/dds 和 www.analog.com/clock.

多通道、10位、500 MSPS直接數(shù)字頻率合成器

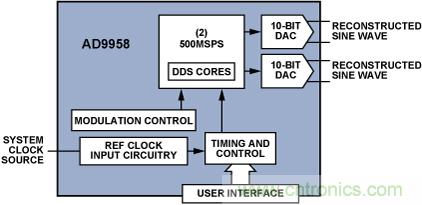

2通道AD9958 (圖5)和4通道AD9959直接數(shù)字頻率合成器(DDS)內(nèi)置兩個(gè)/四個(gè)10位、500 MSPS電流輸出DAC。所有通道共用同一系統(tǒng)時(shí)鐘,因此本身就具有同步功能;將多個(gè)器件互連可提供更高通道數(shù)。各通道的頻率、相位和幅度可獨(dú)立控制,使器件可校正系統(tǒng)相關(guān)失配。所有參數(shù)可線性掃描;或者可為FSK、PSK或ASK調(diào)制選擇16個(gè)電平。輸出正弦波調(diào)諧具有32位頻率分辨率、14位相位分辨率和10位幅度分辨率。AD9958/AD9959采用1.8 V內(nèi)核電源供電,與3.3 V I/O電源邏輯兼容,功耗為315 mW/540 mW(所有通道開啟和 13 mW 掉電模式。額定溫度范圍為–40°C至+85°C,采用56引腳LFCSP封裝,千片訂量報(bào)價(jià)為20.48/37.59美元/片。

圖5. AD9958功能框圖。

12 LVPECL/24 CMOS輸出時(shí)鐘發(fā)生器

AD9520-x 時(shí)鐘發(fā)生器(圖6)可從單一基準(zhǔn)頻率獲得多達(dá)12個(gè)LVPECL或24個(gè)CMOS時(shí)鐘。由于集成了內(nèi)置VCO的完整PLL、可編程分頻器和可配置的輸出緩沖器,該器件實(shí)現(xiàn)了亞皮秒抖動(dòng)性能。四個(gè)選項(xiàng)為片內(nèi)VCO提供了1.45 GHz至2.95 GHz的中心頻率;第五個(gè)選項(xiàng)采用外部VCO工作,頻率可高達(dá)2.4 GHz。該器件接受高達(dá)250 MHz的一路差分或兩路單端基準(zhǔn)時(shí)鐘,提供四組頻率可達(dá)1.6 GHz的LVPECL時(shí)鐘(每組三個(gè))。可編程分頻器的分頻比為1比32,可為每一組時(shí)鐘設(shè)置輸出頻率和粗調(diào)延遲。各LVPECL輸出可重新配置以提供兩個(gè)250 MHz CMOS輸出。AD9520-x采用3.3 V單電源供電,最大功耗為1.5 W;單獨(dú)的輸出驅(qū)動(dòng)器和電荷泵電源可用于邏輯兼容并支持具有擴(kuò)展調(diào)諧范圍的VCO。器件采用64引腳LFCSP封裝,額定溫度范圍為–40°C至+85°C,千片訂量報(bào)價(jià)為12.65美元/片。

圖6. AD9520功能框圖

參考電路

1. AN-837 Application Note, DDS-Based Clock Jitter Performance vs. DAC Reconstruction Filter Performance.

2. Kester, Walt. The Data Conversion Handbook. Analog Devices. Chapters 6 and 7. 2005.

3. Kester, Walt. High Speed System Applications. Analog Devices. Chapters 2 and 3. 2006.

4. MT-101 Tutorial, Decoupling Techniques.

5. MT-031 Tutorial, Grounding Data Converters and Solving the Mystery of AGND and DGND.

推薦閱讀: