【導(dǎo)讀】現(xiàn)代FPGA是有史以來最復(fù)雜的集成電路之一,它們采用最先進 的晶體管技術(shù)和頂尖的架構(gòu),以實現(xiàn)令人難以置信的靈活性和 最高的性能。隨著時間的推移和技術(shù)的進步,這種復(fù)雜性決定 了,在用FPGA設(shè)計和實現(xiàn)系統(tǒng)時,需要做出某些妥協(xié)。這一點 在電源中最為明顯,F(xiàn)PGA每次更新?lián)Q代,電源都要提高精度、 靈活性、可控性、效率和故障感知能力,還要減小體積。

可能有些讀者會質(zhì)疑本文的標(biāo)題, 乍一看,說“FPGA的護理和喂養(yǎng)(care and feeding)”似乎完全不合適。然而,對于這種反對意見的答案很簡單:英語是一個有趣的語言。雖然人們對于“care and feeding”這一說法何時開始流行莫衷一是,但人們都知道,這個說法起源于簡單的農(nóng)業(yè)時代,目前已經(jīng)被人們普遍使用(濫用),指任何脆弱或不穩(wěn)定的東西。在本文中,這一說法可謂一針見血。雖然對于FPGA是否需要“喂養(yǎng)”, 人們充滿爭議,但我們可以肯定的是,F(xiàn)PGA的確需要“護理”!

FPGA電源要求(解讀數(shù)據(jù)手冊)

工程師應(yīng)該將大部分時間用于編程——他們不希望花費時間和精 力去考慮如何設(shè)計合適的電源。實際上,最佳供電方案就是采用 一種既能滿足項目當(dāng)前需求,又能達(dá)到項目升級發(fā)展需求的,強 大、靈活且行之有效的設(shè)計方案。在此,我們將仔細(xì)考察一些重 要的電源規(guī)格及其含義。

電壓精度

內(nèi)核電源電壓是平衡 FPGA 功耗和性能的、最重要的關(guān)鍵要素之一。規(guī)格文檔給出了一系列可接受的電壓,但總的電壓范圍并不 是問題的全部。與所有事物一樣,需要進行權(quán)衡和優(yōu)化。

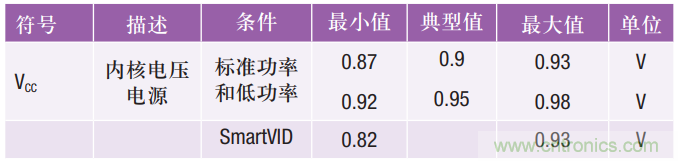

表1是當(dāng)下流行的 Altera Arria 10 FPGA 的內(nèi)核電壓規(guī)格示例。雖然這些數(shù)字是Arria 10特有的數(shù)據(jù),但它們代表了其他 FPGA 內(nèi)核電壓要求。電壓范圍為標(biāo)稱電壓另加±3.3%的容差。在此電壓窗口 內(nèi),F(xiàn)PGA會正常運行,但問題的全貌要復(fù)雜得多。

表1. Altera Arria 10內(nèi)核電壓規(guī)格

注意標(biāo)有“SmartVID”的行,其電壓范圍為 0.82 V 至 0.93 V。這表示,當(dāng) FPGA 通過 SmartVID2 接口(詳見后文)請求自身的內(nèi)核電壓 時,F(xiàn)PGA 可以接受的各種電壓。該 SmartVID 規(guī)格表明了有關(guān) FPGA 的一個基本事實:FPGA 可以在不同電壓下運行,具體取決于其特 定的制造容差以及采用的特定邏輯設(shè)計。FPGA的靜態(tài)電壓可能各不相同。電源必須具備響應(yīng)和適應(yīng)能力。

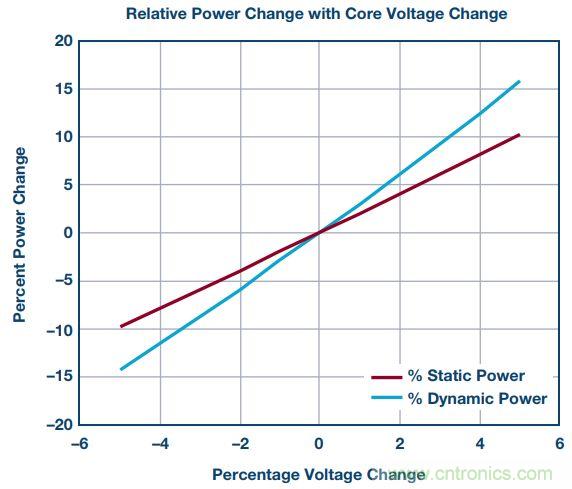

設(shè)計目標(biāo)是產(chǎn)生恰好能滿足編程功能需求的性能水平,不消耗不必要的功率。根據(jù)半導(dǎo)體的物理特性以及 Altera、Xilinx®(圖1)和 其他公司公布的數(shù)據(jù)可知,動態(tài)和靜態(tài)功率會隨著內(nèi)核 VDD 的增加而顯著提高,因此我們的目標(biāo)是確保,給 FPGA 提供的電壓剛好達(dá)到其時序要求即可。功耗過大無助于提高性能。實際上,功耗過多會使情況變得更糟,因為晶體管泄漏電流隨著溫度的升高而增加,從而消耗更多不必要的功率。由于這些原因,當(dāng)務(wù)之急是優(yōu) 化設(shè)計和工作點的電壓。

圖1. Xilinx Virtex V功率與內(nèi)核VCC。

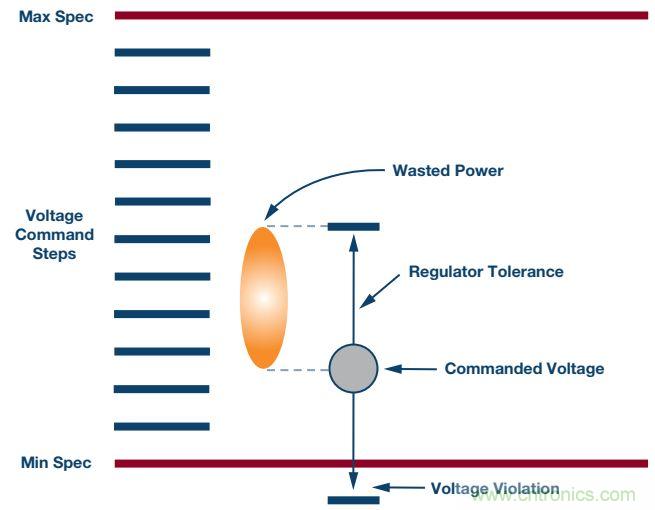

這種優(yōu)化過程需要非常精確的電源才能獲得成功。必須將調(diào)節(jié)器 誤差納入誤差預(yù)算,并從可用于優(yōu)化的可用電壓范圍中減去。如 果內(nèi)核電壓降至要求電壓以下,則FPGA可能因時序錯誤而發(fā)生 故障。如果內(nèi)核電壓漂移至最大規(guī)格值以上,結(jié)果可能會損壞 FPGA,或者可能會在邏輯中形成保持時間故障。為了防止所有 這些情況,必須考慮電源容差范圍,并且指令電壓必須保持在 規(guī)格限值以內(nèi)。

問題是大多數(shù)電源調(diào)節(jié)器都不夠準(zhǔn)確。調(diào)節(jié)電壓可能是指令電壓 容差范圍內(nèi)的任何電壓,可能隨負(fù)載條件、溫度和老化而漂移。 保證 ±2% 容差的電源可以在 4% 的電壓窗口內(nèi)任意調(diào)節(jié)電壓。為 了補償電壓可能比下限值低2% 的問題,必須將指令電壓提高到 比時序要求 2%的水平。如果調(diào)節(jié)器然后漂移到比指令電壓高 2% 的水平,它將在比該工作點所需的最小電壓高 4% 的水平運行。這仍然符合FPGA的指定電壓要求,但卻浪費了大量功率(圖2)。

圖2. 電源調(diào)節(jié)器容差權(quán)衡。

解決辦法是選擇能支持更嚴(yán)格的電壓容差的電源調(diào)節(jié)器。容差 為±0.5%的調(diào)節(jié)器可以在要求工作頻率下,在更接近最小規(guī)格要 求的范圍內(nèi)工作,并且保證與所需電壓的偏離幅度小于1%。這 種情況下,F(xiàn)PGA會正常工作,并且其功耗將達(dá)到該工作條件下 的最低水平。

LTC388x 系列電源控制器可在較寬的可配置電壓范圍內(nèi),保證調(diào) 節(jié)輸出電壓容差優(yōu)于±0.5%。LTC297x 系列電源系統(tǒng)管理器可保證 調(diào)整后的電壓調(diào)節(jié)器容差優(yōu)于±0.25%。在這些精度條件下,對于FPGA,顯然都能使其功耗與性能之間達(dá)到最佳平衡。

熱管理

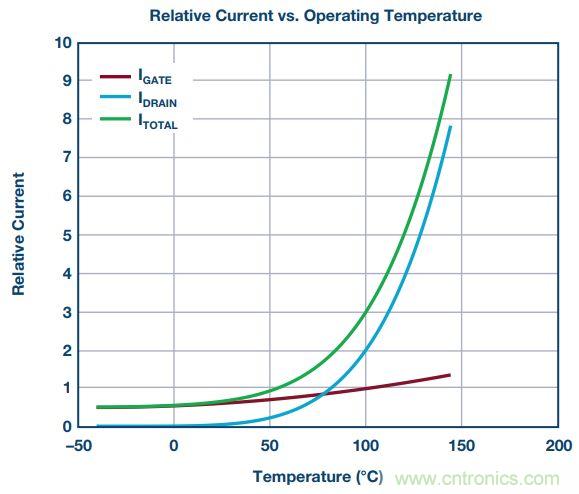

就電源精度而言,一個更微妙的意義體現(xiàn)在熱預(yù)算當(dāng)中。由于靜 態(tài)功耗遠(yuǎn)遠(yuǎn)沒有達(dá)到可以忽略不計的程度,因此FPGA即使在無所 事事的情況下也會升溫。溫度升高會導(dǎo)致更多的靜態(tài)功耗,從而 進一步提高工作溫度(圖3)。向電源添加不必要的電壓只會使該 問題變得更加糟糕。不準(zhǔn)確的電源需要工作電壓保護段,確保有 足夠的電壓來完成此項工作。由容差、系統(tǒng)組件變化和工作溫度 的變化引起的電源電壓不確定性可能產(chǎn)生明顯高于所需最小值的 電壓。當(dāng)施加到FPGA時,這種額外的電壓可能導(dǎo)致熱效應(yīng),甚至 可能在高處理負(fù)載下導(dǎo)致熱失控。

圖3. 電源電流與工作溫度的關(guān)系。

補救措施是選擇一種非常精確的電源,該電源僅產(chǎn)生恰當(dāng)且不超過必要的電壓,這正是 ADI 電源系統(tǒng)管理 (PSM) 器件所擅長的。

SmartVID

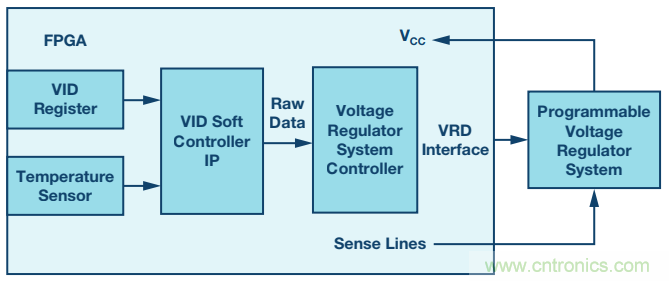

SmartVID 是 Altera 公司出品的一種技術(shù),該技術(shù)用于按照FPGA本身 的要求,為每個 FPGA 提供最佳電壓。FPGA 內(nèi)部有一個寄存器,其 中包含一個因器件而異的電壓(已在出廠中編程),可保證 FPGA 高效運行。FPGA 內(nèi)部編譯的一項IP功能可以讀取該寄存器,并通過 外部總線向電源發(fā)出請求,要求提供這個精確的電壓(圖4)。一 旦達(dá)到電壓要求,它就會在運行期間保持靜止。

圖4. Altera SmartVID結(jié)構(gòu)。

SmartVID 應(yīng)用對電源的要求包括特定的總線協(xié)議、電壓精度和速 度??偩€協(xié)議是 FPGA 用于將其所需電壓傳送到功率調(diào)節(jié)器的幾 種方法之一。在可用的方法中,PMBus 最為靈活,因為它可以 滿足最廣泛的電源管理IC的需求。SmartVID IP 使用兩個 PMBu s指令:VOUT_MODE 和VOUT_COMMAND,用于命令符合 PMBus 標(biāo)準(zhǔn)的功率調(diào)節(jié)器達(dá)到正確的電壓。

調(diào)節(jié)器的電壓精度和速度要求包括自主引導(dǎo)電壓(在PMBus激活之 前),能每10毫秒接受一個新電壓指令,在電壓調(diào)整階段每 10 毫秒能步進 10 mV,并且能在10毫秒的步進時間內(nèi)穩(wěn)定在目標(biāo)電壓30 mV (~3%)范圍內(nèi),最終升至指令電壓并在FPGA工作期間保持靜止。

雖然 Altera 使用的是 SmartVID 技術(shù),但業(yè)界使用的其他類似技術(shù)也 可以完成相同的任務(wù)。一種最簡單的方法是在工廠測試每塊電路板,并在電源的非易失性存儲器中編程一個精確的電壓,優(yōu)化該 特定電路板的性能。使用該技術(shù)時,不需要進一步干預(yù),電源就能在正確的電壓下工作。這是搭載EEPROM 的電源管理器或控制 器的優(yōu)點之一。

LTC388x 系列電源控制器可滿足 Altera SmartVID 的所有要求。此外,LTM4675/LTM4676/LTM4677 µModule 調(diào)節(jié)器可以輕松滿足這些 要求,而且通過單一緊湊的形式提供了完整的解決方案。

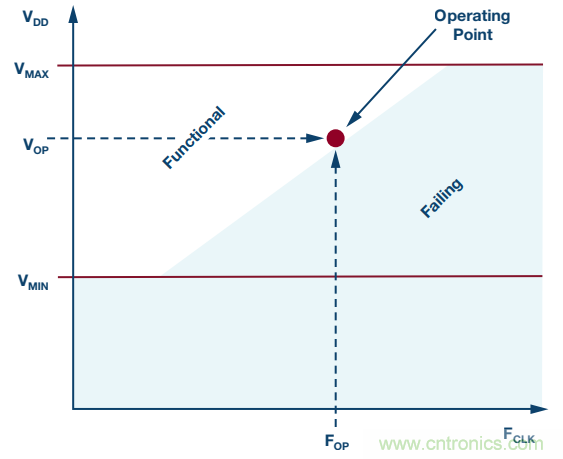

時序收斂

任何邏輯模塊的計算速度均取決于其電源電壓。在限值范圍內(nèi), 電壓越高,性能越快。我們已經(jīng)看到,為什么不能采用簡單的辦 法,即在最高電壓下運行,保證獲得最佳速度。另一方面,我們必須使工作電壓足夠高,能滿足應(yīng)用需求,如圖5所示。

圖5. FPGA工作頻率與VDD之間的平衡關(guān)系。

圖5的一個重要啟示是,當(dāng)特定設(shè)計達(dá)不到其邏輯時序要求并處 于故障區(qū)域時可以采取哪些措施。通常,在將設(shè)計轉(zhuǎn)化成硬件 之前,很難準(zhǔn)確定義正常工作與故障之間的界限,也無法預(yù)先 確定它將在哪個特定電壓下超過時序要求。唯一的選擇是提前確 定一個遠(yuǎn)高于最小值的電壓,以浪費功率為代價來保證功能;或 者設(shè)計一種靈活的電源,以在測試時適應(yīng)硬件需求,甚至在采用 SmartVID 技術(shù)的情況下,能在加電時適應(yīng)硬件需求。適應(yīng)未知需 求的能力使得 ADI PSM 器件的精度更具價值,因為 FPGA 設(shè)計師可以在實際設(shè)計階段和任何開發(fā)階段在功耗與性能之間進行權(quán)衡。

推薦閱讀: